# **Freescale Semiconductor**

**Application Note**

AN4110 Rev. 1, 12/2011

# MSC8157/8 Design Checklist

This application note identifies resources and provides guidance for developing applications using the MSC8157/8 DSP devices. It includes a check list for design phases of projects that incorporate the MSC8157/8 DSPs, including:

- Definition phase. This document highlights MSC8157/8 design requirements, such as pin multiplexing, reset timing, and other design considerations.

- Design implementation phase. This document reviews relevant issues for schematic development and testing.

#### **NOTE**

The MSC8157/8 family includes the following products:

- MSC8157

- MSC8157E

- MSC8158

- MSC8158E

#### Contents

| 1.  | Background                                    |    |

|-----|-----------------------------------------------|----|

| 2.  | Supporting Documentation                      |    |

| 3.  | Power Supply Requirements                     |    |

| 4.  | Power-Up Sequence                             |    |

| 5.  | Boot                                          | 1  |

| 6.  | Clocking Guidelines                           | 1: |

| 7.  | I/O Multiplexing                              | 1  |

| 8.  | Connectivity Guidelines                       | 2  |

| 9.  | Boundary Scan                                 | 4  |

| 10. | Identifying the Device ID and Revision Number | 4  |

| 11  | Signals Connection Summary                    | 4  |

Background

# 1 Background

Developing a project that integrates one or more MSC8157/8 devices requires planning that identifies:

- The specific interfaces required for the design.

- How the interfaces are used including whether the interfaces use dedicated signal lines or must share signal lines during device initialization and/or operation (signal multiplexing).

- How the device is initialized/booted during normal operation.

After identifying the high-level system requirements, the designer must define the following hardware requirements:

- Basic power system

- Clocking system

- Reset/initialization system

- Power-up/start-up sequencing system

- Required memory and memory interface system

- Interface connections

- Disposition of unused signal connections to minimize power consumption.

To support the hardware configuration, the designer must also provide software (not discussed in this document) to support device operation, including:

- Device initialization software (reset sequence, booting, and interface setup).

- Interrupt service routines (ISRs) to handle normal DSP core intervention tasks and error interrupts/exceptions.

- Protocol-defined data management and processing software (which may include standard Ethernet frame processing or any of several vocoder implementations, security algorithms for security-enabled devices, and so forth).

- Other software, such as power-management and reporting or overall process management, as required.

The device specific reference manual and core subsystem reference manuals supply the configuration programming information required to develop the application-specific system environment as well as data transfer management and coprocessor execution. The core reference manual provides detailed programming information required to develop the application-specific algorithm core processing software including ISR processing. Support can be provided or recommended by Freescale Semiconductor. Contact your local sales office or representative for additional information.

# 2 Supporting Documentation

The MSC8157/8 devices are supported by the following types of documentation:

- *Product brief.* Device specific document that includes a high-level description of critical performance metrics, detailed lists of product features, and an overview of available hardware and software development environment tools.

- Data sheet. Device specific document that provides a general description of product features, functional block diagrams, signal/pin assignment for the device packaging, detailed physical and electrical specifications including operating parameter values, general hardware design guidelines, ordering information, and detailed packaging specifications.

- Reference manuals. Each device is supported by four reference manuals:

- Device specific reference manual. Includes detailed information about the device for each module/subsystem with specific programming models to allow configuration, programming, and operation monitoring. In addition, this document describes device level functionality including interrupt processing and debugging.

- *SC3850 DSP Core Reference Manual*. Includes a detailed description of core functionality and operation including the core instruction set programming.

- SC3850 DSP Core Subsystem Reference Manual. Includes a detailed description and programming information for the memory management unit (MMU), extended programmable interrupt controller (EPIC), and internal memories (including cache memories) supported in each subsystem.

- QUICC Engine Block Reference Manual with Protocol Interworking. Includes a detailed description and programming information for the QUICC Engine subsystem including the dual RISC processors, internal memory, communication controllers and interfaces, baud rate generators and counters, and lists which components in this subsystem are used by the MSC8157/8 DSPs.

- Application notes. Individual documents that provide specific recommendations and guidelines for configuration and operation of the device for specific applications or for specific interface enablement and optimization.

#### NOTE

Before starting an application design, refer to the latest device errata document for the corresponding device, currently available under NDA. Contact your local sales office or representative for details.

# 3 Power Supply Requirements

The following sections discuss the various aspects to consider for power supply selection and design.

### 3.1 Power Supply and Ground Inputs

Each MSC8157/8 device requires the power supplies and grounds listed in **Table 1**. Refer to the device specific technical data sheet for minimum and maximum voltage levels.

Table 1. MSC8157/8 Power Inputs

| Signal Name                         | Symbol                                                            | Description                                                                                        | Nominal Voltage |

|-------------------------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------|

|                                     |                                                                   | POWER                                                                                              | •               |

| VDD                                 | $V_{DD}$                                                          | Core supply voltage                                                                                | 1.0 V           |

| PLL0_AVDD<br>PLL1_AVDD<br>PLL2_AVDD | V <sub>DDPLL0</sub><br>V <sub>DDPLL1</sub><br>V <sub>DDPLL2</sub> | System PLL supply voltage                                                                          |                 |

| M3VDD                               | $V_{DDM3}$                                                        | Power for the upper 2 MB of M3 memory. Power can be disabled and 1 MB of M3 memory remains active. |                 |

| CPRIVDD                             | V <sub>DDCPRI</sub>                                               | CPRI supply voltage. Power can be disabled.                                                        |                 |

| CRPEVDD                             | V <sub>DDCRPE</sub>                                               | CRPE supply voltage. Power can be disabled.                                                        |                 |

| MAVDD                               | $V_{DDPLLM}$                                                      | DDR PLL supply voltage                                                                             |                 |

| SXCVDD                              | $V_{DDSXC}$                                                       | SerDes core supply voltage                                                                         |                 |

| SD_PLL1_AVDD<br>SD_PLL2_AVDD        | $V_{DDPLL}$                                                       | SerDes PLL supply voltage                                                                          |                 |

| SXPVDD                              | $V_{DDSXP}$                                                       | SerDes pad voltage                                                                                 | 1.5 V           |

| GVDD                                | $V_{	extsf{DDDDR}}$                                               | DDR memory supply voltage                                                                          |                 |

| MVREF                               | $MV_REF$                                                          | DDR reference voltage                                                                              | = GVDD x 0.5 V  |

| NVDD                                | $V_{DDIO}$                                                        | RGMII and GPIO supply voltage                                                                      | 2.5 V           |

| QVDD                                | $V_{DDIO}$                                                        | I/O clocks, reset, and JTAG supply voltage                                                         |                 |

|                                     |                                                                   | GROUND                                                                                             |                 |

| VSS                                 | GND                                                               | System Ground                                                                                      | 0 V             |

| SD_PLL1_AGND<br>SD_PLL2_AGND        | GND <sub>SDPLL1</sub><br>GND <sub>SDPLL2</sub>                    | SerDes PLL 1 and 2 Ground                                                                          |                 |

| SXCVSS                              | GND <sub>SXC</sub>                                                | SerDes Core Ground                                                                                 |                 |

| SXPVSS                              | GND <sub>SXP</sub>                                                | SerDes Pad Ground                                                                                  |                 |

5

### 3.2 Unused Power Supplies

Some applications which do not use some of the device modules can minimize power consumption by not activating the power supply. **Table 2** summarizes the connection for unused power supply signals.

- If the CPRI is not used, CPRIVDD can be tied to GND.

- If the MAPLE-B2 CRPE is not used, CRPEVDD can be tied to GND.

- If the upper 2048 KB of M3 memory is not used, M3VDD can be tied to GND. The other 1024 KB of M3 memory remains active.

- If the DDR interface is not used, GVDD and MVREF can be left unconnected.

| Module         | Signal Name | Connection |

|----------------|-------------|------------|

| CPRI           | CPRIVDD     | GND        |

| CRPE           | CRPEVDD     | GND        |

| M3 2048 KB     | M3VDD       | GND        |

| DDR Controller | MVREF, GVDD | NC         |

**Table 2. Unused Module Supply Signals**

### 3.3 Power Supply Decoupling

When developing a specific board design, include decoupling capacitors to minimize noise propagation and maintain proper power levels. It is very important that particular attention is paid to decoupling for the supplies for the PLL circuits to minimize radiated emissions and promote stable frequency generation and clocking. Refer to **Section 3.4**, *Global PLL Power Supply Design Considerations* and **Section 3.5**, *SerDes PLL Power Supply Design Considerations* for decoupling guidelines for the global PLL and SerDes PLL power circuits. As a reference, one can review the schematic design of the MSC8157/8ADS, available under NDA from Freescale. The ADS board design includes:

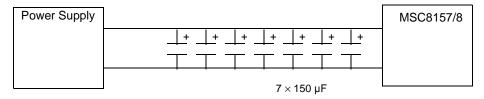

• Bulk capacitors for  $V_{DD}$ . The bulk capacitors decrease low frequency voltage spikes on  $V_{DD}$ . In the case of the MSC8157/8ADS board, seven 150  $\mu$ F capacitors are placed close to the MSC8157/8 device as shown in **Figure 1**.

Figure 1. Bulk Capacitors Placement for MSC8157/8

- Bulk Capacitors for V<sub>DDDDR</sub>. Two 47 μF bulk capacitors are placed on V<sub>DDDDR</sub> in the MSC8157/8ADS to decrease low frequency voltage spikes.

- Bulk Capacitor for  $V_{DDM3}$ . One 47  $\mu F$  bulk capacitor is placed on  $V_{DDM3}$  in the MSC8157/8ADS to decrease low frequency voltage spikes.

- Bulk Capacitor for V<sub>DDCPRI</sub>. One 47 μF bulk capacitor is placed on V<sub>DDCPRI</sub> in the MSC8157/8ADS to decrease low frequency voltage spikes.

#### **Power Supply Requirements**

- Bulk Capacitor for V<sub>DDCRPE</sub>. One 47 μF bulk capacitor is placed on V<sub>DDCRPE</sub> in the MSC8157/8ADS to decrease low frequency voltage spikes.

- Bypass Capacitors for all power supplies on the MSC8157/8ADS. 0.01  $\mu$ F, 0.1  $\mu$ F, 1  $\mu$ F, 4.7  $\mu$ F with low ESR/ESL are used for filtering high frequency noise.

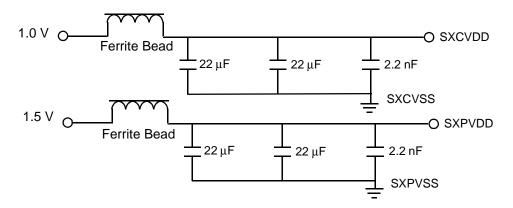

- **Figure 2** shows the SerDes core SXCVDD and pad SXPVDD filter circuits. The SXCVSS and SXPVSS can be joined to a low noise, solid reference ground plane. It is recommended that noise coupling simulation be performed on actual PCB design implementation. The target noise specification is:

- Maximum noise on SerDes core (SXCVDD, SXCVSS) and SerDes pad (SXPVDD, SXPVSS) supply is 15 mV peak-to-peak

Figure 2. SXCVDD and SXPVDD Supplies

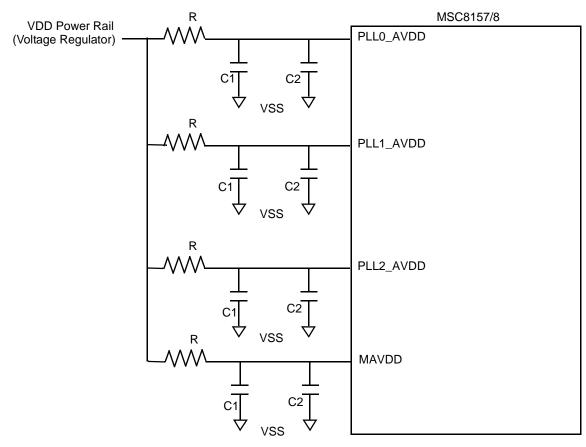

### 3.4 Global PLL Power Supply Design Considerations

Each global PLL power supply must have an external RC filter for the PLL*n*\_AVDD input (see **Figure 3**) where:

- $R = 5 \Omega \pm 5\%$

- C1 = 10  $\mu$ F  $\pm$  10%, 0603, X5R, with ESL  $\leq$  0.5 nH, low ESL Surface Mount Capacitor.

- C2 = 1.0  $\mu$ F ± 10%, 0402, X5R, with ESL ≤ 0.5 nH, low ESL Surface Mount Capacitor.

A higher capacitance value for C2 may be used to improve the filter as long as the other C2 parameters do not change. All three PLLs can connect to a single supply voltage source (such as a voltage regulator) as long as the external RC filter is applied to each PLL separately. For optimal noise filtering, place the circuit as close as possible to PLLn\_AVDD inputs.

Figure 3. PLL Supplies

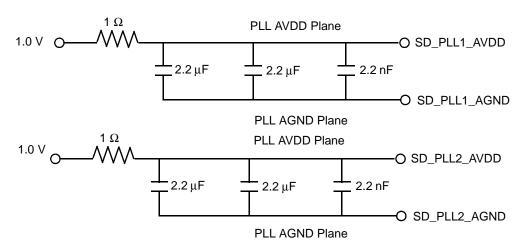

# 3.5 SerDes PLL Power Supply Design Considerations

The SerDes PLL power supply must be filtered using a circuit similar to the one shown in **Figure 4** to ensure stability of the internal clock. All traces should be kept short, wide and direct. Use separate islands/wide traces for each PLL bank's SD\_PLLn\_AVDD and SD\_PLLn\_AGND connections. The ground islands/wide traces of individual PLL banks should be joined to a single ground plane either through an inductor or through a zero-ohm resistance. While it is possible to connect the power islands together to a single supply via a resistor or a ferrite bead, it is recommended to have multiple power islands as close to the source and as far away from the DSP as possible. Do not place any digital or other bank traces near the PLL power and ground planes.

For maximum effectiveness, the filter circuit should be placed as close as possible to the SD\_PLLn\_AVDD ball to ensure it filters out as much noise as possible. The ground connection should be near the SD\_PLLn\_AGND ball. To provide effective bypass capacitance at high frequencies, these two islands/wide traces should be directly over each other and on the nearest PCB layer, that is, layers 3 and 4 of a 6 layer board. The capacitors are connected from the SD\_PLLn\_AVDD to the ground plane. Only surface mount technology (SMT) capacitors should be used to minimize inductance. Connections from all capacitors to power and ground should be done with multiple vias to reduce inductance further. The 2.2 nF capacitor is placed closest to the package pin, followed by the two 2.2  $\mu$ F capacitors, and finally the 1  $\Omega$  resistor to the board supply plane.

#### **Power Supply Requirements**

The capacitors are connected from SD\_PLL*n*\_AVDD to the ground plane. The 2.2 nF decoupling capacitor should be within about 0.5 cm of each power pin. The target noise specification is:

Maximum noise on SerDes PLL (SD\_PLLn\_AVDD, SD\_PLLn\_AGND) is 25 mV peak-to-peak

Figure 4. SerDes PLL Supply

## 3.6 DDR PLL Power Supply Design Considerations

The DDR PLL power supply must have an external RC filter for the MAVDD input (see **Figure 3**) where:

- $R = 5 \Omega \pm 5\%$

- C1 = 10  $\mu$ F  $\pm$  10%, 0603, X5R, with ESL  $\leq$  0.5 nH, low ESL Surface Mount Capacitor.

- C2 = 1.0  $\mu$ F ± 10%, 0402, X5R, with ESL ≤ 0.5 nH, low ESL Surface Mount Capacitor.

A higher capacitance value for C2 may be used to improve the filter as long as the other C2 parameters do not change. For optimal noise filtering, place the circuit as close as possible to the MAVDD inputs.

# 3.7 Remote Power Supply Sensing

To assure consistency of input power levels, some applications use a practice of connecting the remote sense signal input of an on-board power supply to one of power supply pins of the IC device. The advantage of using this connection is the ability to compensate for the slow components of the IR drop caused by resistive supply current path from on-board power supply to the pins layer on the package. However, because of specific device requirements, not every ball connection can be selected as the remote sense pin. Some of these pins must be connected to the appropriate power supply or ground to ensure correct device functionality. Some connections supply critical power to a specific high usage area of the IC die; using such a connection as a non-supply pin could impact necessary supply current during high current events. The following balls can be used as the board supply remote sense output without degrading the power and ground supply quality:

- VDD: G7, H18

- *VSS*: H7, H17, AB13

Do not use any other connections for remote sensing. Use of any other connections for this purpose can result in application and device failure.

# 4 Power-Up Sequence

The following sections describe the required device initialization sequence.

# 4.1 Power Supply Coupling and Sequence

Use the following guidelines for coupling the power supplies:

- Couple the M3VDD, CPRIVDD and CRPEVDD with the VDD power rail using an extremely low impedance path.

- Couple the PLL0\_AVDD, PLL1\_AVDD, PLL2\_AVDD and MAVDD with the VDD power rail using an RC filter as shown in **Figure 3**.

- Couple inputs SD\_PLL*n*\_AVDD with SXCVDD power rail respectively using an RC filter as shown in **Figure 4**.

- Since MVREF = 0.5 \* GVDD, see step 2 of the power-on sequence of the power rails below.

External voltage applied to any input line must not exceed the I/O supply voltage related to this line by more than 0.6 V at any time, including during power-up. Some designs require pull-up voltages applied to selected input lines during power-up for configuration purposes. This is an acceptable exception to the rule during start-up. However, each such input can draw up to 80 mA per input pin per MSC8157/8 device in the system during power-up. An assertion of the inputs to the high voltage level before power-up should be with slew rate less than 4 V/ns.

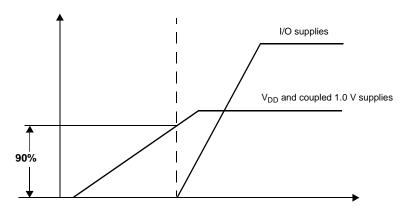

The device power rails should rise in the following sequence as shown in **Figure 5**:

- 1. VDD and all coupled 1.0 V supplies (M3VDD, CPRIVDD, CRPEVDD, PLL0\_AVDD, PLL1\_AVDD, PLL2\_AVDD, MAVDD)

- 2. After the above supplies rise to 90% of their nominal value, the following I/O power rails may rise in any sequence: QVDD, NVDD, GVDD and MVREF coupled one to another.

Figure 5. V<sub>DD</sub> and I/O supplies Power-on Sequence

There is no dependency in power-up/power-down sequence between the GVDD, NVDD, and QVDD power rails. There is also no dependency in power-up/power-down sequence between the SerDes supplies SXCVDD and SXPVDD and other MSC8157/8 supplies. All supplies must be at their stable values within 50 ms as shown in Table 3 on page 11.

**Power-Up Sequence**

#### 4.2 Clock, Reset, and Supply Coordination

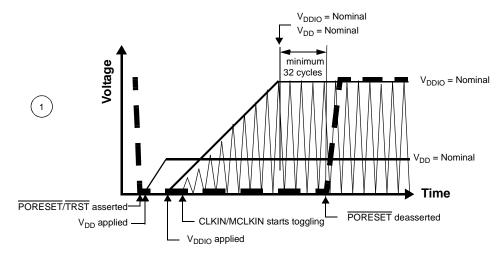

Starting the device requires coordination between several inputs including: clock, reset, and power supplies. Follow these ramp-up guidelines when starting up an MSC8157/8 device:

- 1. PORESET and TRST must be asserted externally for the duration of the supply ramp-up, using the V<sub>DDIO</sub> supply. TRST deassertion does not have to be synchronized with PORESET deassertion. However, TRST must be deasserted before normal operation begins to ensure correct functionality of the device.

- 2. V<sub>DD</sub> is applied and ramps up. See **Section 4.3**, *Power-On Ramp Time* for the required ramp rate.

- 3. V<sub>DDIO</sub> is applied and ramps up. See **Section 4.3**, *Power-On Ramp Time* for the required ramp rate.

- 4. CLKIN/MCLKIN starts toggling. It should swing within the V<sub>DDIO</sub> range during V<sub>DDIO</sub> ramp-up, so its amplitude grows as V<sub>DDIO</sub> grows during ramp-up.

- 5. CLKIN/MCLKIN should toggle at least 32 cycles before PORESET deassertion to guarantee correct device operation. The 32 cycles should only be counted from the time after V<sub>DDIO</sub> reaches its nominal value.

- 6. PORESET is deasserted.

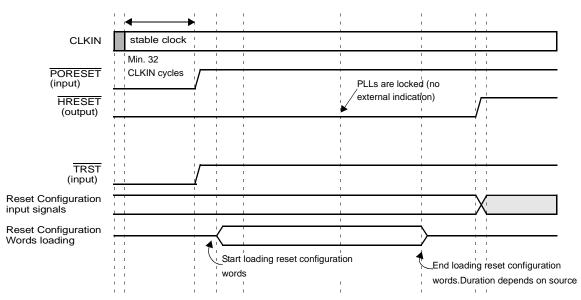

**Figure 6** shows a sequence in which  $V_{DDIO}$  ramps up after  $V_{DD}$  and CLKIN/MCLKIN begins toggling as the  $V_{DDIO}$ supply rises.

Figure 6. Supply Ramp-Up Sequence

MSC8157/8 Design Checklist, Rev. 1 10 Freescale Semiconductor

#### 4.3 **Power-On Ramp Time**

The power-on ramp rate applies to all voltage supplies (including GVDD/SXPVDD/SXCVDD/QVDD/GVDD/NVDD, all VDD supplies, MVREF, and all AVDD supplies). Controlling the maximum power-on ramp time is required to avoid falsely triggering the ESD circuitry. **Table 3** defines the power supply ramp rate and time specification.

| Parameter                                                                               | Min | Max   | Unit |

|-----------------------------------------------------------------------------------------|-----|-------|------|

| Required ramp rate                                                                      | _   | 36000 | V/s  |

| Required ramp time.                                                                     | _   | 50    | ms   |

| Note: 4 December 1 is a selficion of the selficion of the selficion of the selficion of |     |       |      |

Note: Ramp period is specified as a linear ramp from 10% to 90% of nominal voltage of the specific voltage supply.

All MCKE signals must remain low during the power up sequence.

#### 4.4 **Reset Connectivity**

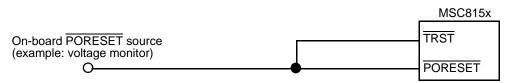

When a debugger is not used, implement the connection scheme shown in **Figure 7**. PORESET and TRST can be tied together.

Figure 7. Reset Connection in Functional Application

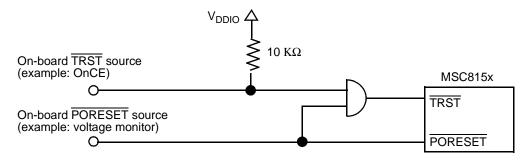

When a debugger is used, implement the connection scheme shown in **Figure 8**.

Figure 8. Reset Connection in Debugger Application

#### **HRESET IN Usage** 4.5

The HRESET\_IN signal allows resetting of the MSC8157/8 device without evoking hard reset of other devices that are connected in the same HRESET IN chain. In a multiprocessor system, the HRESET IN pin can be optionally used instead of the HRESET pin to allow individual reset. It can also be used to allow individual reset over the JTAG interface.

MSC8157/8 Design Checklist, Rev. 1 Freescale Semiconductor 11

**Power-Up Sequence**

#### 4.6 Reset Flow

The reset process and the reset configuration word (RCW) are described in detail in **Chapter 5**, *Reset* in the device specific reference manual.

A full reset is started by asserting the PORESET signal. The signal must remain asserted for a minimum time that is specified in the device specific technical data sheet. The contents of the RCW determine how the device is initialized and selects the basic I/O multiplexing mode, clock mode, and boot method. The reset configuration signals must be driven to the correct levels and held for the minimum time specified in the technical data sheet after the PORESET signal is deasserted. The reset sequence includes assertion of HRESET.

After HRESET is deasserted, it can take 62000 OCN cycles (500 MHz clock) for the SerDes block (HSSI) to exit reset and lock its internal PLL. The user should poll the HSSI\_SR[SERDES1\_RST\_DONE] and HSSI\_SR[SERDES2\_RST\_DONE] bits to determine when the SerDes reset is complete if the relevant PLL is enabled. See the High Speed Serial Interface Status Register (HSSI\_SR) description in **Chapter 8**, *General Configuration Registers* of the device specific reference manual for details.

The individual configuration signal selection determines the overall timing for the reset sequences, as described in **Chapter 5**, *Reset* in the reference manual. The HRESET signal is both an input and an output and can be asserted by external input or by software. An application can use these reset sequences to initialize specific internal device structures. Once asserted the MSC8157/8 device controls when the signals are deasserted based on the hard reset sequence, as defined in the reference manual.

#### NOTE

HRESET is an open-drain input/output pin. Make sure you use a pull-up resistor. After the initial assertion by an external host, make sure that the host releases the signal so that the MSC8157/8 device can deassert the signal. When using HRESET, use **Table 5-2** Reset Actions for Each Reset Source in the device specific reference manual to verify that the selected signal supports the required reset functionality. Calculate and check the expected reset process duration. See **Section 5.2.3** Reset Configuration Input Signal Selection and Reset Sequence Duration in the device reference manual for details.

Figure 9. Power-On Reset Flow

# 4.7 Reset Configuration Word

See Section 5.2.2 Reset Configuration Word Source in the device specific reference manuals for details about selecting the reset configuration input settings. Depending on the selected RCW source, use the following guidelines to assure proper device initialization:

- Using the information from **Section 5.2.2** *Reset Configuration Word Source* in the reference manual, select the correct RCW\_SRC[0–2] combination that fits your design.

- You must use external pull up or pull down resistors in order to set the correct values of the RCW\_SRC and RC signals during the PORESET flow. You must not rely on the internal pull up inside the GPIO signals for this purpose.

- If you are using the I<sup>2</sup>C interface with a single EEPROM to initialize more than one MSC8157/8 device, use the connection guidelines given in **Chapter 5**, *Reset* of the reference manual. Verify that you are correctly connecting the I2C\_SDA and I2C\_SCL signal lines and are providing correct sequencing for asserting and deasserting the STOP\_BS signal for each device.

- If RC[21–0] are used, make sure that the design supports the correct values during the reset sequence and then switches to required levels to support the configured functionality as GPIO, IRQ or DMA external signals. See **Chapter 5**, *Reset* of the device specific reference manual to see how the RC signals are used to define the RCW.

- If one of the two hard coded RCW is being used, make sure that RCW\_SRC[0-2] has relevant setting for your configuration. See **Chapter 5**, *Reset* of the device specific reference manual for the hard-coded options for the RCW.

Boot

#### NOTE

Pay special attention to a configuration in which the signals RC[0–3] are being used during loading of the RCW in the multiplexed RCW loading mode (RCW\_SRC[0–2] = 000) to a device and the device is configured as a reset master (RCWHR[RM] = 1). In such configuration the device will be using one or more of the GPIO[0–3] signals (which are shared with RC[0–3]) during its boot sequence to drive the STOP\_BS of the reset slaves in the system (see **Section 5.2.1.5** *Loading Multiple Devices From a Single I*<sup>2</sup>*C EEPROM* for more details) so the values driven on the RC[0–3] during the device  $\overline{PORESET}$  sequence must be disconnected before the device start to drive the GPIO[0–3] signals in order to avoid contention. This can be done using tri-state buffers as in the example shown in the device specific reference manual in **Chapter 5**, *Reset*, **Section 5.2.5.2** *Loading Multiplexed RCW from External Pins* (RCW\_SRC[0–2] = 000).

• If the application relies on loading RCW from I<sup>2</sup>C EEPROM, consider how to initialize the I<sup>2</sup>C EEPROM on a board fresh out of the assembly that is presumably filled with all 1s. To initialize I<sup>2</sup>C EEPROM, the MSC8157/8 must be reset properly using another reset configuration such as the RC[21–0] signal lines or one of the two hard coded RCWs.

For additional information, see also:

• *Using an I<sup>2</sup>C EEPROM During MSC8157 Initialization* (AN4205)

# 5 Boot

The boot process completes the initialization by setting up the selected interfaces and subsystems and loading the basic processing and data management software. **Chapter 6**, *Boot Program* in the reference manual gives a detailed description of the boot process for each possible boot scenario.

The boot program initializes the MSC8157/8 after it completes a reset sequence. The MSC8157/8 can boot from an external host through the RapidIO interface or download a user boot program through the I<sup>2</sup>C, SPI, or Ethernet ports. The default boot code is located in an internal 96 KB ROM at 0xFEF00000–0xFEF17FFF and is accessible to all cores. For readability, the internal boot code is written in C and is based on the Freescale SmartDSP OS. Refer to **Chapter 6**, *Boot Program* in the device-specific reference manual for boot details.

The boot port is determined by the RCWHR[BPRT] field as listed in **Table 4**.

**Boot Port** RCWHR[BPRT] Description I<sup>2</sup>C I<sup>2</sup>C 0000 RapidIO interface 0001 RapidIO interface without I<sup>2</sup>C 0010 RapidIO interface with I<sup>2</sup>C SPI SPI 0011 RGMII1 0100 RGMII1 without I<sup>2</sup>C 0110 RGMII1 with I2C SGMII1 0101 SGMII1 without I2C SGMII1 with I2C 0111

**Table 4. Boot Port Select**

MSC8157/8 Design Checklist, Rev. 1

| Table 4. Boot Port S | Select (co | ontinued) |

|----------------------|------------|-----------|

|----------------------|------------|-----------|

| Boot Port | RCWHR[BPRT]                | Description                     |

|-----------|----------------------------|---------------------------------|

| SGMII2    | 1001                       | SGMII2 without I <sup>2</sup> C |

|           | 1011                       | SGMII2 with I <sup>2</sup> C    |

| _         | 1000<br>1010<br>1100– 1111 | Reserved                        |

**Chapter 6,** *Boot Program* of the device specific reference manual describes the functionality and operation of the boot program. You must consider the following guidelines with regard to the boot program:

- The MSC8157/8 boot code uses the lower 25 KB of M3 memory starting from 0xC0000000. Make sure that the user boot code/application code that is being loaded to memory does not overwrite this memory space.

- Remember that MSC8157/8 uses both data cache (DCache) and instruction cache (ICache). If you download code to MSC8157/8 memory and there is valid data in the cache, the core uses the data from the cache. Use the INVALIDATE command on all caches (L1 ICache and DCache and L2 Cache) to ensure that the core reads updated data.

- If you are using an MMU setting during the boot or application download, remember to clear/update the MMU setting after the download is completed.

- After boot, all unused HSSI lanes should be powered down. Only used HSSI lanes should be powered up. Refer to **Section 8.1.6**, *HSSI Specific Lane Is Not Used on page 28* for connectivity of unused lanes.

For additional information, see:

- Using an I<sup>2</sup>C EEPROM During MSC8157 Initialization (AN4205)

- MSC81xx Ethernet Boot Test (AN3436)

# 6 Clocking Guidelines

The following sections provides guidelines and descriptions for the various clocking systems used with and in the MSC8157/8.

### 6.1 Clock Signals

MSC8157/8 devices use clock signals for internal clocking and for synchronous interfaces. Each of the clock signals has its own unique requirements. **Table 5** shows the clock signals.

Table 5. MSC8157/8 Clock Signals

| Module  | Signal Name     | Signal Description                         |

|---------|-----------------|--------------------------------------------|

| General | CLKIN           | Clock input to the MSC8157/8 PLLs          |

|         | CLKOUT          | Clock output of PLL                        |

| SerDes  | SD_REF_CLK[1-2] | SerDes reference clock. Differential pair. |

|         | SD_REF_CLK[1-2] |                                            |

MSC8157/8 Design Checklist, Rev. 1

#### **Clocking Guidelines**

Table 5. MSC8157/8 Clock Signals (continued)

| Module           | Signal Name | Signal Description                  |

|------------------|-------------|-------------------------------------|

| Timers           | TMR0:TMR6   | Timer input or output               |

| JTAG             | TCK         | JTAG test clock                     |

| DDR              | MCLKIN      | Optional clock input to the DDR PLL |

|                  | MCK0:MCK2   | DDR clock. Differential pair.       |

|                  | MCK0:MCK2   |                                     |

| QUICC Engine     | GE1_RX_CLK  | Ethernet 1 receive clock            |

|                  | GE1_TX_CLK  | Ethernet 1 transmit clock           |

|                  | GE1_GTX_CLK | Ethernet 1 output transmit clock    |

|                  | GE2_RX_CLK  | Ethernet 2 receive clock            |

|                  | GE2_TX_CLK  | Ethernet 2 transmit clock           |

|                  | GE2_GTX_CLK | Ethernet 2 output transmit clock    |

|                  | GE_MDC      | Ethernet management data clock      |

| SPI              | SPI_SCK     | SPI clock                           |

| I <sup>2</sup> C | I2C_SCL     | I <sup>2</sup> C clock              |

Refer to the device specific technical data sheet in for the individual signals requirements. For each clock signal, make sure that you comply with each of the following specifications:

- Clock frequency limits

- Clock slope limits

- Jitter limits

- Output clock load requirements

- Clock tree for the DDR-SDRAM balancing with zero delay buffers for large loads

- Special startup sequencing requirements for clock signals during reset

Refer to the individual functional block sections in the device specific reference manual for specific clock guidelines.

#### 6.2 Clock Mode

As shown in **Chapter 7**, *Clocks* in the device-specific reference manual, the MSC8157/8 device has a flexible clocking scheme to deliver the clock frequencies used by the various subsystems and external interfaces. During power-on reset, the user configures a specific clock mode that defines the various clock frequencies and domains in the device. The specific clock mode is selected using the MODCK[5–0] field in the Reset Configuration Word Low Register (RCWLR). **Figure 7-1** in the device specific reference manual shows the relationships between the input clock (CLKIN), the optional DDR input clock (MCLKIN) and the mode (MODCK), and the internal clock domains.

Note that for each MODCK selected, a specific frequency is selected for each clock domain, and a CLKIN frequency of 133.333 MHz is required. **Table 7-1** in the device specific reference manual lists detailed information about the MODCK options. Evaluate each clock and make sure that CLKIN frequency and clock mode (MODCK) yield the desired internal frequencies as listed in **Table 7-2**.

#### 6.3 Clock Mode Tool

A spreadsheet tool that calculates all component frequencies depending clock mode and clock source for the MSC8157/8 DSPs is available under NDA. This tool also validates configured clock schemes by clock specifications.

### 6.4 Clock and Timing Signal Board Layout Considerations

When laying out the system board, use the following guidelines:

- Keep clock and timing signal paths as short as possible and route with 50  $\Omega$  impedance for single-ended signals and 100  $\Omega$  impedance for differential signals.

- Use a serial termination resistor placed close to the clock buffer to minimize signal reflection. Use the following equation to calculate the resistor value:

$$R_{term} = R_{im} - R_{buf}$$

where  $R_{im}$  = trace characteristic impedance and

$$R_{buf}$$

= clock buffer internal impedance.

#### 6.5 Unused Internal Clocks

The following section provides additional information about the individual subsystems to minimize power consumption and noise on the PCB buses in cases when one or more of the device subsystems is not used by the application.

### 6.5.1 DDR Memory Controller

In addition to providing proper termination for the unused DDR signal lines, the user should also set SCCR[DDRDIS] to disable the clock to the DDR controller.

In order to reduce DDR IO power consumption when the DDR controller is not in use, the user should set the DDR I/O into sleep mode in the DDR\_GCR[DDR\_DOZE]. This should be performed as soon as possible after PORESET sequence end.

# 6.5.2 QUICC Engine Subsystem

In addition to providing proper termination for the unused Ethernet and SPI signal lines, if none of the interfaces are used, you should also set SCCR[QEDIS] to disable the clock to the QUICC Engine subsystem. See **Chapter 7**, *Clocks* in the reference manual for detailed programming information.

# 6.5.3 HSSI Subsystem

In addition to providing proper termination for unused HSSI signal lines in case non of the HSSI interfaces (Serial RapidIO, PCI Express, SGMII, CPRI) are working (for non of the interfaces to work, RCWLR[SP] should be "0", see **Chapter 5**, *Reset* in the reference manual for detailed programming information) you should also set SCCR[HSSIDIS] to disable the clock to the HSSI sub system. See **Chapter 7**, *Clocks* in the reference manual for detailed programming information.

Freescale Semiconductor

MSC8157/8 Design Checklist, Rev. 1

I/O Multiplexing

#### 6.5.4 **CLKOUT**

If CLKOUT is not used, set RCWLR[CLKO] = 11 and RCWLR[P3V] = 0 in order to configure CLKOUT to be always "low". See **Chapter 5**, *Reset* and **Chapter 7**, *Clocks* in the reference manual for detailed programming information.

# 7 I/O Multiplexing

The MSC8157/8 devices support two groups of I/O configurations:

- SerDes Multiplexing

- MSC8157/E: 2 Serial RapidIO interfaces, PCI Express interface, 2 SGMII interfaces and 6 lanes CPRI sharing the SerDes interface (10 lanes total).

- MSC8158/E: 2 Serial RapidIO interfaces, 2 SGMII interfaces and 6 lanes CPRI sharing the SerDes interface (8 lanes total).

- Selected during power-on reset by the RCWLR[SP] bits in the low part of the Reset Configuration Word (see **Chapter 5**, *Reset* for details).

- GPIO Multiplexing

- GPIOs are shared with IRQs, external DMA, Timers, UART, SPI, I<sup>2</sup>C and CPRI

- Configured by GPIO configuration registers (see **Chapter 21**, *GPIO* for details).

Based on the system requirements, select the required interfaces, including external DDR memory, and the type of memory to be used. Refer to the pin-multiplexing tool that is available under NDA. Contact your local sales office or representative for details. This tool helps to define which interfaces can be selected simultaneously. See **Section 7.4** *Pin Multiplexing Tool* in this document for details

MSC8157/8 Design Checklist, Rev. 1

### 7.1 MSC8157 SerDes (HSSI) Multiplexing

The Serial RapidIO, PCI Express, SGMII, and CPRI signals are multiplexed on the 10 lanes of the SerDes interface on the MSC8157.

The required combination of interfaces is selected during power-on reset by the RCWLR[SP] bits in the low portion of the Reset Configuration Word. Table 6 describes the functionality of each lane of the HSSI ports, depending on the selected protocol. The number next to # specifies the controller number and the number between () specifies the lane number. Note the restrictions associated with the various RCWLR[SP] modes.

Note that there may be restrictions in some HSSI multiplexing modes as shown in the exceptions column. For example, in modes where RapidIO and SGMII are used, the RapidIO controller cannot operate at 3.125 GHz unless the SGMII is disabled by software.

SerDes Lanes RCWLR[SP] Mode **Exceptions** Protocol Select Α В C D Ε G Н J None 0000000 0 PEX(0) PEX(1) PEX(2) PEX(3) **CPRI CPRI CPRI CPRI CPRI CPRI** None 0000001 1 #6 #5 #4 #3 #2 #1 **SGMII CPRI CPRI CPRI CPRI CPRI CPRI** PEX(0) PEX(1) **SGMII** None 0000101 5 #1 #2 #6 #5 #4 #3 #2 #1 CPRI RIO **CPRI CPRI CPRI** CPRI CPRI RIO **SGMII** PEX(0) 1, 3 0000110 6 #2(1) #2(0) #6 #2 #5 #4 #3 #2 #1 PEX(0) RIO **SGMII SGMII CPRI CPRI CPRI CPRI CPRI CPRI** 1, 3 7 0000111 #2(0) #1 #2 #6 #5 #4 #3 #2 #1 RIO RIO RIO RIO **CPRI CPRI CPRI CPRI CPRI CPRI** None 0001010 10 #2(0) #2(1) #2(2) #2(3) #6 #5 #4 #3 #2 #1 RIO RIO **SGMII SGMII CPRI CPRI CPRI CPRI CPRI CPRI** 1, 3 0001011 11 #2(0) #2(1) #2 #3 **CPRI** RIO RIO **SGMII** RIO **CPRI CPRI CPRI CPRI CPRI** 1, 2, 3 0001100 12 #2(0) #2(1) #1 #1(0) #6 #5 #4 #3 #2 #1 RIO RIO RIO RIO **CPRI CPRI CPRI CPRI CPRI CPRI** 0001101 13 #2(0) #2(1) #1(1) #1(0) RIO **SGMII SGMII** RIO **CPRI CPRI CPRI CPRI CPRI CPRI** 1, 2, 3 0001110 14 #2(0) #2 #1 #1(0) #6 #5 #4 #3 #2 #1 PEX(1) PEX(3) SGMII **SGMII** CPRI **CPRI CPRI CPRI** PEX(0) PEX(2) None 0010001 17 #1 RIO RIO SGMII **SGMII CPRI CPRI CPRI CPRI** PEX(0) PEX(1) 1, 3 0010011 19 #2(0) #2(1) #1 #2 #4 #3 #2 #1 **CPRI CPRI CPRI CPRI** PEX(1) RIO RIO RIO RIO PEX(0) 1.2.3 0010100 20 #2(0) #2(1) #1(0) #1(1) **Exceptions** RIO cannot run at 3.125 GHz. unless SGMII is powered down by software. 2. If 3.125 GHz RIO is required, both RIO controllers must run at the same frequency. 3. Boot from RIO at 3.125 GHz is not supported. Boot from RIO at frequencies other than 3.125 GHz is not supported.

Table 6. MSC8157 HSSI Multiplexing

#### MSC8157/8 Design Checklist, Rev. 1

#### I/O Multiplexing

Table 6. MSC8157 HSSI Multiplexing

| RCWLR[SP]          |      | SerDes Lanes         |                     |                 |                       |                     |                                  |                      |                     |                    |              |                   |

|--------------------|------|----------------------|---------------------|-----------------|-----------------------|---------------------|----------------------------------|----------------------|---------------------|--------------------|--------------|-------------------|

| Protocol<br>Select | Mode | Α                    | В                   | С               | D                     | E                   | F                                | G                    | Н                   | I                  | J            | Exceptions        |

| 0010110            | 22   | PEX(0)               | PEX(1)              | RIO<br>#1(0)    | RIO<br>#1(1)          | RIO<br>#1(2)        | RIO<br>#1(3)                     | CPRI<br>#4           | CPRI<br>#3          | CPRI<br>#2         | CPRI<br>#1   | 1, 3              |

| 0011101            | 29   | RIO<br>#2(0)         | RIO<br>#2(1)        | RIO<br>#2(2)    | RIO<br>#2(3)          | RIO<br>#1(0)        | SGMII<br>#2                      | CPRI<br>#4           | CPRI<br>#3          | CPRI<br>#2         | CPRI<br>#1   | 1, 2, 3           |

| 0011110            | 30   | RIO<br>#2(0)         | RIO<br>#2(1)        | RIO<br>#2(2)    | RIO<br>#2(3)          | RIO<br>#1(0)        | RIO<br>#1(1)                     | CPRI<br>#4           | CPRI<br>#3          | CPRI<br>#2         | CPRI<br>#1   | 2                 |

| 0011111            | 31   | RIO<br>#2(0)         | RIO<br>#2(1)        | SGMII<br>#1     | SGMII<br>#2           | RIO<br>#1(0)        | RIO<br>#1(1)                     | CPRI<br>#4           | CPRI<br>#3          | CPRI<br>#2         | CPRI<br>#1   | 1, 2, 3           |

| 0100011            | 35   | PEX(0)               | PEX(1)              | PEX(2)          | PEX(3)                | SGMII<br>#1         | SGMII<br>#2                      | RIO<br>#1(0)         | RIO<br>#1(1)        | CPRI<br>#2         | CPRI<br>#1   | 1, 3              |

| 0100100            | 36   | PEX(0)               | PEX(1)              | PEX(2)          | PEX(3)                | RIO<br>#1(0)        | RIO<br>#1(1)                     | RIO<br>#1(2)         | RIO<br>#1(3)        | CPRI<br>#2         | CPRI<br>#1   | 1, 3              |

| 0100101            | 37   | PEX(0)               | PEX(1)              | SGMII<br>#1     | SGMII<br>#2           | RIO<br>#2(1)        | RIO<br>#2(0)                     | RIO<br>#1(0)         | RIO<br>#1(1)        | CPRI<br>#2         | CPRI<br>#1   | 1, 2, 3           |

| 0101000            | 40   | RIO<br>#2(0)         | RIO<br>#2(1)        | RIO<br>#2(2)    | RIO<br>#2(3)          | SGMII<br>#1         | SGMII<br>#2                      | CPRI<br>#4           | CPRI<br>#3          | CPRI<br>#2         | CPRI<br>#1   | 1, 3              |

| 0101110            | 46   | PEX(0)               | PEX(1)              | RIO<br>#2(0)    | RIO<br>#2(1)          | RIO<br>#1(0)        | RIO<br>#1(1)                     | RIO<br>#1(2)         | RIO<br>#1(3)        | CPRI<br>#2         | CPRI<br>#1   | 1, 2, 3           |

| 0110000            | 48   | PEX(0)               | PEX(1)              | SGMII<br>#1     | SGMII<br>#2           | RIO<br>#1(0)        | RIO<br>#1(1)                     | RIO<br>#1(2)         | RIO<br>#1(3)        | CPRI<br>#2         | CPRI<br>#1   | 1, 3              |

| 0111101            | 61   | RIO<br>#2(0)         | RIO<br>#2(1)        | RIO<br>#2(2)    | RIO<br>#2(3)          | SGMII<br>#1         | SGMII<br>#2                      | RIO<br>#1(0)         | RIO<br>#1(1)        | CPRI<br>#2         | CPRI<br>#1   | 1, 2, 3           |

| 1000001            | 65   | RIO<br>#2(0)         | RIO<br>#2(1)        | RIO<br>#2(2)    | RIO<br>#2(3)          | RIO<br>#1(0)        | RIO<br>#1(1)                     | RIO<br>#1(2)         | RIO<br>#1(3)        | CPRI<br>#2         | CPRI<br>#1   | 2                 |

| 1000010            | 66   | PEX(0)               | PEX(1)              | PEX(2)          | PEX(3)                | RIO<br>#2(1)        | RIO<br>#2(0)                     | RIO<br>#1(0)         | RIO<br>#1(1)        | RIO<br>#1(2)       | RIO<br>#1(3) | 1, 2, 3           |

| 1000101            | 69   | PEX(0)               | PEX(1)              | PEX(2)          | PEX(3)                | SGMII<br>#1         | SGMII<br>#2                      | RIO<br>#2(1)         | RIO<br>#2(0)        | RIO<br>#1(0)       | RIO<br>#1(1) | 1, 2, 3           |

| 1010001            | 81   | PEX(0)               | PEX(1)              | PEX(2)          | PEX(3)                | SGMII<br>#1         | RIO<br>#2(0)                     | RIO<br>#1(0)         | RIO<br>#1(1)        | RIO<br>#1(2)       | RIO<br>#1(3) | 1, 2, 3           |

| 1010011            | 83   | PEX(0)               | PEX(1)              | PEX(2)          | PEX(3)                | SGMII<br>#1         | SGMII<br>#2                      | RIO<br>#1(0)         | RIO<br>#1(1)        | RIO<br>#1(2)       | RIO<br>#1(3) | 1, 3              |

| 1010100            | 84   | PEX(0)               | PEX(1)              | PEX(2)          | PEX(3)                | SGMII<br>#1         | SGMII<br>#2                      | RIO<br>#1(0)         | RIO<br>#1(1)        | RIO<br>#1(2)       | RIO<br>#1(3) | 1, 4              |

| 1010101            | 85   | PEX(0)               | PEX(1)              | SGMII<br>#1     | SGMII<br>#2           | RIO<br>#2(1)        | RIO<br>#2(0)                     | RIO<br>#1(0)         | RIO<br>#1(1)        | RIO<br>#1(2)       | RIO<br>#1(3) | 1, 3              |

| 1100110            | 102  | RIO<br>#2(0)         | RIO<br>#2(1)        | RIO<br>#2(2)    | RIO<br>#2(3)          | RIO<br>#1(0)        | RIO<br>#1(1)                     | RIO<br>#1(2)         | RIO<br>#1(3)        | SGMII<br>#1        | SGMII<br>#2  | 1, 2, 3           |

| Excepti            | ons  | 1.<br>2.<br>3.<br>4. | If 3.125<br>Boot fr | GHz R<br>om RIO | IO is req<br>at 3.125 | uired, bo<br>GHz is | inless So<br>oth RIO<br>not supp | controlle<br>oorted. | oowered<br>ers must | down by run at the | ne same      | re.<br>frequency. |

The frequency of each protocol is configured in the RCWLR as shown below. Refer to the reference manual for more details on the protocol frequency.

• RCWLR[R1FREQ] selects the frequency for the RapidIO port 1

- RCWLR[R2FREQ] selects the frequency for the RapidIO port 2

- RCWLR[PFREQ] selects the frequency for the PCI Express

- RCWLR[CFREQ] selects the frequency for the CPRI

- RCWLR[SCLK1, SCLK2] select the SerDes reference clock

### 7.2 MSC8158/E SerDes (HSSI) Multiplexing

The Serial RapidIO, SGMII and CPRI signals are multiplexed on the 8 lanes of the SerDes interface on the MSC8158/E.

The needed combination of interfaces is selected during power-on reset by the RCWLR[SP] bits in the low portion of the Reset Configuration Word. Table 7 describes the functionality of each lane of the HSSI ports, depending on the selected protocol. The number next to # specifies the controller number and the number between () specifies the lane number. Note the restrictions associated with the various RCWLR[SP] modes.

Note that there may be restrictions in some HSSI multiplexing modes as shown in the exceptions column. For example, in modes where RapidIO and SGMII are used, the RapidIO controller cannot operate at 3.125 GHz unless the SGMII is disabled by software.

**SerDes Lanes** RCWLR[SP] Mode **Exceptions** Protocol Select C F D Ε Н J G None 0000000 0 CPRI#6 CPRI#5 CPRI#4 CPRI#3 CPRI#2 CPRI#1 None 0000001 1 **SGMII SGMII** CPRI#6 CPRI #5 CPRI#4 CPRI#3 CPRI#2 CPRI#1 None 0000101 5 #2 #1 **SGMII** CPRI#6 CPRI#5 CPRI#4 CPRI#3 CPRI#2 CPRI#1 1, 2 0000110 6 #2 **SGMII SGMII** CPRI#6 CPRI #5 CPRI#4 CPRI#3 CPRI#2 CPRI#1 1, 2 7 0000111 #1 #2 CPRI#6 CPRI#5 CPRI#4 CPRI#3 CPRI#2 CPRI#1 None 0001010 10 **SGMII SGMII** CPRI#6 CPRI #5 CPRI#4 CPRI#3 CPRI#2 CPRI#1 1, 2 0001011 11 #2 SGMII RIO CPRI#6 CPRI#1 CPRI#5 CPRI#4 CPRI#3 CPRI#2 1. 2 0001100 12 #1(0) #1 RIO RIO CPRI#6 CPRI#5 CPRI#4 CPRI#3 CPRI#2 CPRI#1 None 0001101 13 #1(1) #1(0) SGMII RIO CPRI#6 CPRI#5 CPRI#4 CPRI#3 CPRI#2 CPRI#1 1, 2 0001110 #1(0) **Exceptions** RapidIO interface cannot run at 3.125 GHz. 1. Boot from RapidIO interface at 3.125 GHz is not supported. RIO #2 is powered down by boot. If needed, this controller should be powered up by the user code according to the power up sequence requirements. If 3.125 GHz RapidIO interface is required, both RapidIO controllers must run at the same

Table 7. MSC8158 HSSI Multiplexing

#### MSC8157/8 Design Checklist, Rev. 1

frequency

#### I/O Multiplexing

### Table 7. MSC8158 HSSI Multiplexing (continued)

| RCWLR[SP]       | Ml - | SerDes Lanes   |              |                                       |                                          |                                         |                                           |                          |              |                                  |  |

|-----------------|------|----------------|--------------|---------------------------------------|------------------------------------------|-----------------------------------------|-------------------------------------------|--------------------------|--------------|----------------------------------|--|

| Protocol Select | Mode | С              | D            | E                                     | F                                        | G                                       | Н                                         | I                        | J            | Exceptions                       |  |

| 0010001         | 17   | _              | _            | SGMII<br>#1                           | SGMII<br>#2                              | CPRI #4                                 | CPRI #3                                   | CPRI #2                  | CPRI #1      | None                             |  |

| 0010010         | 19   | _              | _            | SGMII<br>#1                           | SGMII<br>#2                              | CPRI #4                                 | CPRI #3                                   | CPRI #2                  | CPRI #1      | 1, 2                             |  |

| 0010011         | 20   | RIO<br>#2(0)   | RIO<br>#2(1) | RIO<br>#1(0)                          | RIO<br>#1(1)                             | CPRI #4                                 | CPRI #3                                   | CPRI #2                  | CPRI #1      | 2, 3, 4                          |  |

| 0010110         | 22   | RIO<br>#1(0)   | RIO<br>#1(1) | RIO<br>#1(2)                          | RIO<br>#1(3)                             | CPRI #4                                 | CPRI #3                                   | CPRI #2                  | CPRI #1      | None                             |  |

| 0011101         | 29   | _              | _            | RIO<br>#1(0)                          | SGMII<br>#2                              | CPRI #4                                 | CPRI #3                                   | CPRI #2                  | CPRI #1      | 1, 2                             |  |

| 0011110         | 30   | _              | _            | RIO<br>#1(0)                          | RIO<br>#1(1)                             | CPRI #4                                 | CPRI #3                                   | CPRI #2                  | CPRI #1      | None                             |  |

| 0011111         | 31   | SGMII<br>#1    | SGMII<br>#2  | RIO<br>#1(0)                          | RIO<br>#1(1)                             | CPRI #4                                 | CPRI #3                                   | CPRI #2                  | CPRI #1      | 1, 2                             |  |

| 0100011         | 35   | _              | _            | SGMII<br>#1                           | SGMII<br>#2                              | RIO<br>#1(0)                            | RIO<br>#1(1)                              | CPRI #2                  | CPRI #1      | 1, 2                             |  |

| 0100100         | 36   | _              | _            | RIO<br>#1(0)                          | RIO<br>#1(1)                             | RIO<br>#1(2)                            | RIO<br>#1(3)                              | CPRI #2                  | CPRI #1      | None                             |  |

| 0100101         | 37   | SGMII<br>#1    | SGMII<br>#2  | RIO<br>#2(1)                          | RIO<br>#2(0)                             | RIO<br>#1(0)                            | RIO<br>#1(1)                              | CPRI #2                  | CPRI #1      | 1, 2, 3                          |  |

| 0101000         | 40   | _              | _            | SGMII<br>#1                           | SGMII<br>#2                              | CPRI #4                                 | CPRI #3                                   | CPRI #2                  | CPRI #1      | 1, 2                             |  |

| 0101110         | 46   | _              | _            | RIO<br>#1(0)                          | RIO<br>#1(1)                             | RIO<br>#1(2)                            | RIO<br>#1(3)                              | CPRI #2                  | CPRI #1      | None                             |  |

| 0110000         | 48   | SGMII<br>#1    | SGMII<br>#2  | RIO<br>#1(0)                          | RIO<br>#1(1)                             | RIO<br>#1(2)                            | RIO<br>#1(3)                              | CPRI #2                  | CPRI #1      | 1, 2                             |  |

| 0111101         | 61   | _              | _            | SGMII<br>#1                           | SGMII<br>#2                              | RIO<br>#1(0)                            | RIO<br>#1(1)                              | CPRI #2                  | CPRI #1      | 1, 2                             |  |

| 1000001         | 65   | _              | _            | RIO<br>#1(0)                          | RIO<br>#1(1)                             | RIO<br>#1(2)                            | RIO<br>#1(3)                              | CPRI #2                  | CPRI #1      | None                             |  |

| 1000010         | 66   | _              | _            | _                                     | _                                        | RIO<br>#1(0)                            | RIO<br>#1(1)                              | RIO<br>#1(2)             | RIO<br>#1(3) | None                             |  |

| 1000101         | 69   | _              | _            | SGMII<br>#1                           | SGMII<br>#2                              | _                                       | _                                         | RIO<br>#1(0)             | RIO<br>#1(1) | 1, 2                             |  |

| 1010001         | 81   | _              | _            | SGMII<br>#1                           | _                                        | RIO<br>#1(0)                            | RIO<br>#1(1)                              | RIO<br>#1(2)             | RIO<br>#1(3) | 1, 2                             |  |

| 1010011         | 83   | _              | _            | SGMII<br>#1                           | SGMII<br>#2                              | RIO<br>#1(0)                            | RIO<br>#1(1)                              | RIO<br>#1(2)             | RIO<br>#1(3) | 1, 2                             |  |

| 1010100         | 84   | _              | _            | SGMII<br>#1                           | SGMII<br>#2                              | RIO<br>#1(0)                            | RIO<br>#1(1)                              | RIO<br>#1(2)             | RIO<br>#1(3) | 1, 3                             |  |

| Exception       | ons  | 2.<br>3.<br>4. | user code    | RapidIO in<br>powered do<br>according | terface at 3<br>own by boo<br>to the pow | 3.125 GHz<br>ot. If neede<br>er up sequ | is not supp<br>d, this cont<br>ence requi | troller shou<br>rements. | ·            | ered up by the<br>un at the same |  |

### MSC8157/8 Design Checklist, Rev. 1

23

|                 |      |                |             |                                         |                                          |                                         | •                                         | •                        |              |                |

|-----------------|------|----------------|-------------|-----------------------------------------|------------------------------------------|-----------------------------------------|-------------------------------------------|--------------------------|--------------|----------------|

| RCWLR[SP]       | Mode | SerDes Lanes   |             |                                         |                                          |                                         |                                           |                          |              |                |

| Protocol Select |      | С              | D           | E                                       | F                                        | G                                       | Н                                         | I                        | J            | Exceptions     |

| 1010101         | 85   | SGMII<br>#1    | SGMII<br>#2 |                                         | _                                        | RIO<br>#1(0)                            | RIO<br>#1(1)                              | RIO<br>#1(2)             | RIO<br>#1(3) | 1, 2           |

| 1100110         | 102  | _              | _           | RIO<br>#1(0)                            | RIO<br>#1(1)                             | RIO<br>#1(2)                            | RIO<br>#1(3)                              | SGMII<br>#1              | SGMII<br>#2  | 1, 2           |

| Exception       | ons  | 2.<br>3.<br>4. | user code   | RapidIO in<br>bowered do<br>according t | terface at 3<br>own by boo<br>to the pow | 3.125 GHz<br>ot. If neede<br>er up sequ | is not supp<br>d, this cont<br>ence requi | troller shou<br>rements. |              | ered up by the |

Table 7. MSC8158 HSSI Multiplexing (continued)

The frequency of each protocol is configured in the RCWLR as shown below. Refer to the reference manual for more details on the protocol frequency.

- RCWLR[R1FREQ] selects the frequency for the RapidIO port 1

- RCWLR[R2FREQ] selects the frequency for the RapidIO port 2

- RCWLR[CFREQ] selects the frequency for the CPRI

- RCWLR[SCLK1, SCLK2] select the SerDes reference clock

### 7.3 **GPIO Multiplexing**

One GPIO signal is dedicated (GPIO22). The remainder of the signals have multiplexed functionality as either GPIO or  $\overline{IRQ}$ , DMA external requests, Timers, UART, SPI, I<sup>2</sup>C, or CPRI. See the product specific reference manual in **Section 3.9** *GPIO/Maskable Interrupt Signal Summary* for details. In addition, some of the GPIO signals are served during the PORESET sequence for configuration. See **Section 3.3** *Reset and Configuration Signals* and **Chapter 5**, *Reset* in the reference manual for details.

#### NOTE

Some GPIO signal lines have specific reset functionality during the reset process and different functionality in normal operation. See **Section 3.3** *Reset and Configuration Signals* in the device reference manual for details. Verify the following with regard to reset signal lines:

- Make sure that the reset signals have the proper value during the reset process and that the alternate functionality is disabled.

- After reset is complete, make sure that the required alternate signal functionality is enabled

- In order to use GPIO input, the corresponding GPIO input pins must be enabled in the GIER register. The default setting is disabled

- If you want to use the GPIO pin as either IRQ, DMA external requests, Timers, UART, SPI, I<sup>2</sup>C or CPRI, you must also program the GPUER and GIER registers to set their correct values. They are not

MSC8157/8 Design Checklist, Rev. 1

#### **Connectivity Guidelines**

automatically set by the settings of the PAR register as dedicated peripheral.

# 7.4 Pin Multiplexing Tool

To validate the pin multiplexing plan and verify the status of all pins for your application, there is a pin multiplexing tool available under NDA. The tool spreadsheet confirms all pin availability based on application requirements, such as DDR memory, peripherals, GPIO/IRQ pins, and so on. In addition, this tool validates power supplies and displays all pin mapping based for the application. Contact your local sales office or representative for details.

# 8 Connectivity Guidelines

Select the pin multiplexing mode to allocate the required I/O signals. Then use the guidelines presented in the following subsections for board design and connections. The following conventions are used in describing the connectivity requirements:

- GND indicates using a  $10 \text{ k}\Omega$  pull-down resistor (recommended) or a direct connection to the ground plane. Direct connections to the ground plane may yield DC current up to 50 mA through the I/O supply that adds to overall power consumption.

- $V_{DD}$  indicates using a 10 k $\Omega$  pull-up resistor (recommended) or a direct connection to the appropriate power supply. Direct connections to the supply may yield DC current up to 50 mA through the I/O supply that adds to overall power consumption.

- Mandatory use of a pull-up or pull-down resistor is clearly indicated as "pull-up/pull-down." For buses, each pin on the bus should have its own resistor.

- NC indicates "not connected" and means do not connect anything to the pin.

- The phrase "in use" indicates a typical pin connection for the required function

### 8.1 Disposition of Unused Signal Lines

Some applications may not use all available MSC8157/8 interfaces. For the unused signal lines, proper system design should include correct termination to achieve the following:

- Allow proper functionality for the device.

- Reduce power consumption.

- Reduce number of signal connection.

- Reduce PCB design complexity.

### 8.1.1 Unused GPIO Signal Connections

Unused GPIO signals should be left not connected, as long as they are not used as their other function (IRQ, DMA external signals, Timers, UART, SPI or  $I^2C$ ). Because all GPIO signals are configured as GPIO with inputs and outputs disabled and the internal  $20 \text{ k}\Omega$  pull up is enabled by default after reset, those that remain unused pins should be left unconnected.

#### 8.1.2 DDR Interface Is Not Used

Table 8. Connectivity of DDR Related Pins When the DDR Interface Is Not Used

| Signal Name | Pin Connection |

|-------------|----------------|

| MCLKIN      | GND            |

| MDQ[0-63]   | NC             |

| MDQS[7-0]   | NC             |

| MDQS[7-0]   | NC             |

| MA[15-0]    | NC             |

| MCK[0-2]    | NC             |

| MCK[0-2]    | NC             |

| MCS[1-0]    | NC             |

| MDM[7-0]    | NC             |

| MBA[2-0]    | NC             |

| MCAS        | NC             |

| MCKE[1-0]   | NC             |

| MODT[1-0]   | NC             |

| MMDIC[1-0]  | NC             |

| MRAS        | NC             |

| MWE         | NC             |

| MECC[7-0]   | NC             |

| MDM8        | NC             |

| MDQS8       | NC             |

| MDQS8       | NC             |

| MAPAR_OUT   | NC             |

#### **Connectivity Guidelines**

Table 8. Connectivity of DDR Related Pins When the DDR Interface Is Not Used (continued)

|                                                                                                                                                                                                                                                                                                                              | Signal Name | Pin Connection |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------|

| MAPAR                                                                                                                                                                                                                                                                                                                        | R_IN        | NC             |

| MVREF                                                                                                                                                                                                                                                                                                                        |             | NC             |

| GVDD                                                                                                                                                                                                                                                                                                                         |             | NC             |

| Note: If the DDR controller is not used, disable the internal DDR clock by setting the appropriate bit in the System Clock Control Register (SCCR) and put all DDR I/O in sleep mode by setting DR_GCR[DDR_DOZE]. See the Clocks and General Configuration Registers chapters in the MSC8157/8 Reference Manual for details. |             |                |

# 8.1.3 DDR Interface Is Used With 32-Bit DDR Memory Only

**Table 9** lists unused pin connection when using 32-bit DDR memory. The 32 most significant data lines are not used.

Table 9. Connectivity of DDR Related Pins When Using 32-bit DDR Memory Only

| Signal Name | Pin Connection |

|-------------|----------------|

| MCLKIN      | optional       |

| MDQ[31-0]   | in use         |

| MDQ[63-32]  | NC             |

| MDQS[3-0]   | in use         |

| MDQS[7-4]   | NC             |

| MDQS[3-0]   | in use         |

| MDQS[7-4]   | NC             |

| MA[15-0]    | in use         |

| MCK[2-0]    | in use         |

| MCK[2-0]    | in use         |

| MCS[1-0]    | in use         |

| MDM[3-0]    | in use         |

| MDM[7-4]    | NC             |

| MBA[2-0]    | in use         |

| MCAS        | in use         |

| MCKE[1-0]   | in use         |

| MODT[1-0]   | in use         |

| MMDIC[1-0]  | in use         |

| MRAS        | in use         |

| MWE         | in use         |

| MVREF       | = GVDD x 0.5 V |

| GVDD        | 1.5 V          |

### 8.1.4 DDR ECC Is Not Used

When the error code correction mechanism is not used in any 32- or 64-bit DDR configuration, refer to **Table 10** to determine the correct pin connections.

Table 10. Connectivity of Unused ECC Mechanism Pins

| Signal Name | Pin connection |

|-------------|----------------|

| MECC[7-0]   | NC             |

| MDM8        | NC             |

| MDQS8       | NC             |

| MDQS8       | NC             |

#### 8.1.5 HSSI Port Is Not Used

The signal names in Table 11 are inclusive names for the SerDes interfaces. For individual pin names refer to Table 12.

Table 11. Connectivity of HSSI Related Pins When No HSSI Lanes Are Used

| Signal Name                                                                                                     | Pin Connection |

|-----------------------------------------------------------------------------------------------------------------|----------------|

| SD_IMP_CAL_RX                                                                                                   | NC             |

| SD_IMP_CAL_TX                                                                                                   | NC             |

| SD_REF_CLK[1-2]                                                                                                 | SXCVSS         |

| SD_REF_CLK[1-2]                                                                                                 | SXCVSS         |

| SD_[A-J]_RXD                                                                                                    | SXCVSS         |

| SD_[A-J]_RXD                                                                                                    | SXCVSS         |

| SD_[A-J]_TXD                                                                                                    | NC             |

| SD_[A-J]_TXD                                                                                                    | NC             |

| SD_PLL[1-2]_AVDD                                                                                                | 1.0 V          |

| SD_PLL[1-2]_AGND                                                                                                | 0 V            |

| SXPVSS                                                                                                          | 0 V            |

| SXCVSS                                                                                                          | 0 V            |

| SXPVDD                                                                                                          | 1.5 V          |

| SXCVDD                                                                                                          | 1.0 V          |

| Note: All lanes in the HSSI SerDes should be powered down. Refer to the MSC8157/8 Reference Manual for details. |                |

**Connectivity Guidelines**

### 8.1.6 HSSI Specific Lane Is Not Used

Removing power to an unused HSSI lane could cause unpredictable voltage levels on lane outputs or a high leakage situation on lane inputs. **Table 12** shows the connectivity when a specific HSSI lane is not used.

Table 12. Connectivity of HSSI Related Pins When a Specific Lane Is Not Used

| Signal Name                                                                                                                                    | Pin Connection                               |

|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| SD_IMP_CAL_RX                                                                                                                                  | Pull up to SXCVDD with 200 $\Omega$ resistor |

| SD_IMP_CAL_TX                                                                                                                                  | Pull up to SXPVDD with 200 $\Omega$ resistor |

| SD_REF_CLK[1-2]                                                                                                                                | In use                                       |

| SD_REF_CLK[1-2]                                                                                                                                | In use                                       |

| SD_[A-J]_RXD                                                                                                                                   | SXCVSS                                       |

| SD_[A-J]_RXD                                                                                                                                   | SXCVSS                                       |

| SD_[A-J]_TXD                                                                                                                                   | NC                                           |

| SD_[A-J]_TXD                                                                                                                                   | NC                                           |

| SD_PLL[1-2]_AVDD                                                                                                                               | 1.0 V                                        |

| SD_PLL[1-2]_AGND                                                                                                                               | 0 V                                          |

| SXPVSS                                                                                                                                         | 0 V                                          |

| SXCVSS                                                                                                                                         | 0 V                                          |

| SXPVDD                                                                                                                                         | 1.5 V                                        |

| SXCVDD                                                                                                                                         | 1.0 V                                        |

| Note: The signal names indicate a signal series. Connectivity guidelines should only be applied for the specific lane/lanes that are not used. |                                              |

### 8.1.7 RGMII Ethernet Is Not Used

Table 13. Connectivity of RGMII Related Pins When the RGMII Interface Is Not Used

| Signal Name | Pin Connection |

|-------------|----------------|

| GE1_RD0     | GND            |

| GE1_RD1     | GND            |

| GE1_RD2     | GND            |

| GE1_RD3     | GND            |

| GE1_RX_CLK  | GND            |

| GE1_RX_CTL  | GND            |

| GE1_TD0     | NC             |

| GE1_TD1     | NC             |

| GE1_TD2     | NC             |

| GE1_TD3     | NC             |

| GE1_TX_CLK  | NC             |

| GE1_TX_CTL  | NC             |

| GE1_GTX_CLK | NC             |

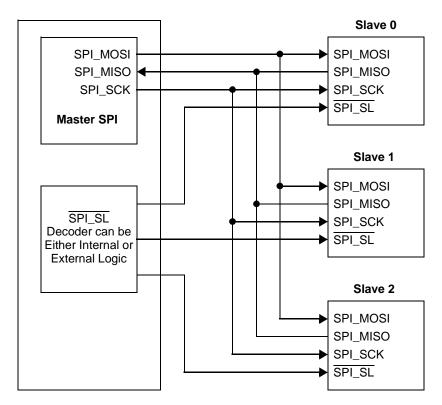

MSC8157/8 Design Checklist, Rev. 1