# SOT1780-3 WI CSP36 wafer law

WLCSP36, wafer level chip-size package; 36 terminals; 0.4 mm pitch; 2.674 mm x 2.822 mm x 0.564 mm body

25 March 2020 Package information

## 1 Package summary

Terminal position code B (bottom)

Package type descriptive code WLCSP36

Package style descriptive code WLCSP (wafer level chip-size package)

Mounting method type S (surface mount)

Issue date 15-04-2016

Manufacturer package code 98ASA00949

Table 1. Package summary

| Parameter                      | Min   | Nom   | Max   | Unit |

|--------------------------------|-------|-------|-------|------|

| package length                 | 2.797 | 2.822 | 2.847 | mm   |

| package width                  | 2.649 | 2.674 | 2.699 | mm   |

| package height                 | -     | 0.564 | 0.599 | mm   |

| nominal pitch                  | -     | 0.4   | -     | mm   |

| actual quantity of termination | -     | 36    | -     |      |

WLCSP36, wafer level chip-size package; 36 terminals; 0.4 mm pitch; 2.674 mm x 2.822 mm x 0.564 mm

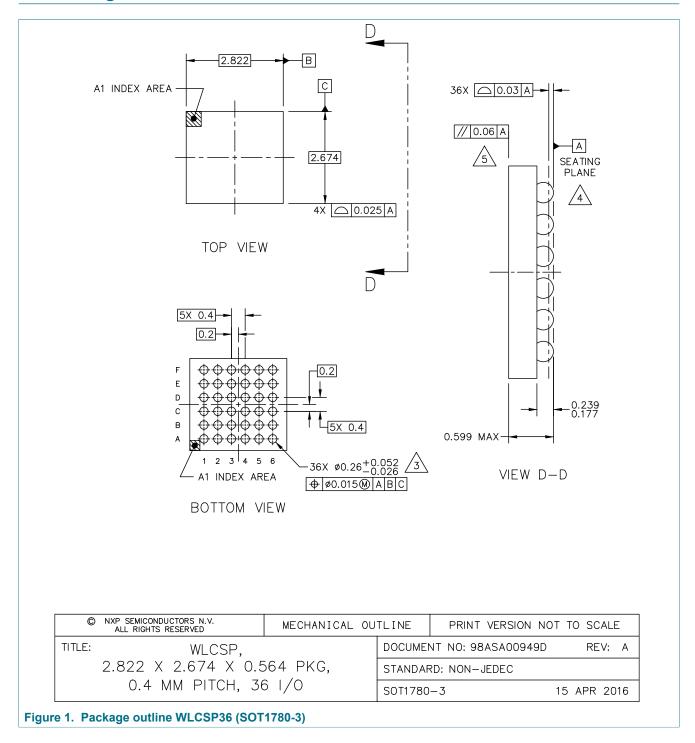

## 2 Package outline

WLCSP36, wafer level chip-size package; 36 terminals; 0.4 mm pitch; 2.674 mm x 2.822 mm x 0.564 mm body

#### NOTES:

- 1. ALL DIMENSIONS IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

3.

MAXIMUM SOLDER BALL DIAMETER MEASURED PARALLEL TO DATUM A.

DATUM A, THE SEATING PLANE, IS DETERMINED BY THE SPHERICAL CROWNS OF THE SOLDER BALLS.

5.

PARALLELISM MEASUREMENT SHALL EXCLUDE ANY EFFECT OF MARK ON TOP SURFACE OF PACKAGE.

| © NXP SEMICONDUCTORS N.V. ALL RIGHTS RESERVED      | MECHANICAL OU | TLINE               | PRINT VERSION NO   | T TO SCALE  |  |

|----------------------------------------------------|---------------|---------------------|--------------------|-------------|--|

| TITLE: WLCSP,                                      |               | DOCUMEN             | NT NO: 98ASA00949D | REV: A      |  |

| 2.822 X 2.674 X 0.564 PKG,<br>0.4 MM PITCH, 36 I/O |               | STANDARD: NON-JEDEC |                    |             |  |

|                                                    |               | SOT1780             | -3                 | 15 APR 2016 |  |

Figure 2. Package outline note WLCSP36 (SOT1780-3)

WLCSP36, wafer level chip-size package; 36 terminals; 0.4 mm pitch; 2.674 mm x 2.822 mm x 0.564 mm

## 3 Legal information

#### **Disclaimers**

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

WLCSP36, wafer level chip-size package; 36 terminals; 0.4 mm pitch; 2.674 mm x 2.822 mm x 0.564 mm body

### **Contents**

| 1 | Package summary1   |

|---|--------------------|

| 2 | Package outline2   |

| 3 | Legal information4 |

Date of release: 25 March 2020