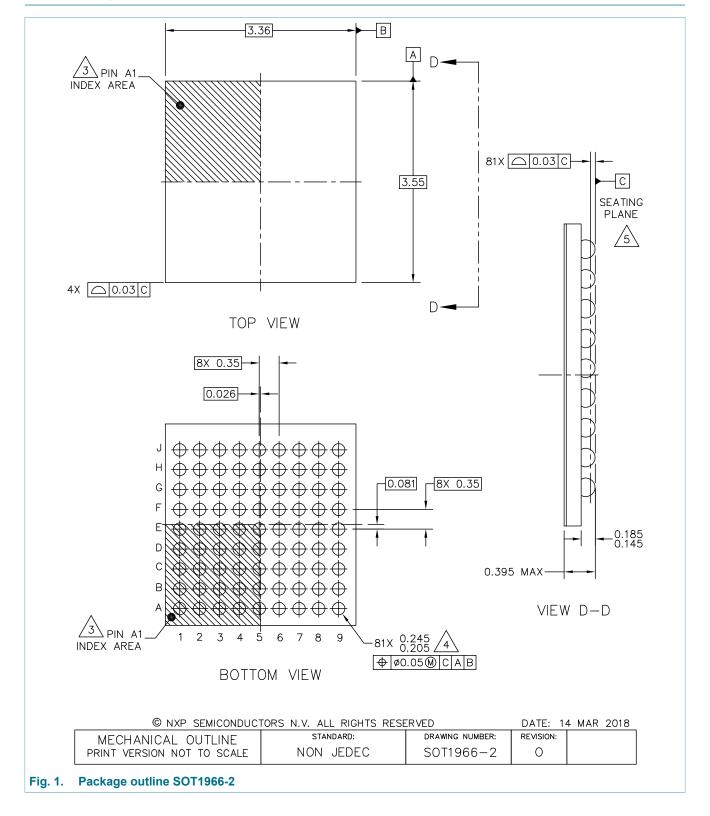

WLCSP81, wafer level chip-scale package; 81 bumps; 0.35 mm pitch, 3.55 mm x 3.36 mm x 0.365 mm body (backside coating included)

6 April 2018

Package information

## 1. Package summary

Terminal position code B (bottom)

Package type descriptive code WLCSP81

Package style descriptive code WLCSP (wafer level chip-size package)

Mounting method type S (surface mount)

Issue date 14-3-2018

Manufacturer package code 98ASA01227D

#### **Table 1. Package summary**

| Symbol         | Parameter                      | Min   | Тур | Nom   | Max   | Unit |

|----------------|--------------------------------|-------|-----|-------|-------|------|

| D              | package length                 | 3.52  | -   | 3.55  | 3.58  | mm   |

| Е              | package width                  | 3.33  | -   | 3.36  | 3.39  | mm   |

| A              | seated height                  | 0.335 | -   | 0.365 | 0.395 | mm   |

| е              | nominal pitch                  | _     | -   | 0.35  | -     | mm   |

| n <sub>2</sub> | actual quantity of termination | _     | -   | 81    | -     | A/A  |

WLCSP81, wafer level chip-scale package; 81 bumps; 0.35 mm pitch, 3.55 mm x 3.36 mm x 0.365 mm body (backside coating included)

# 2. Package outline

WLCSP81, wafer level chip-scale package; 81 bumps; 0.35 mm pitch, 3.55 mm x 3.36 mm x 0.365 mm body (backside coating included)

#### NOTES:

- 1. ALL DIMENSIONS IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

23. PIN A1 FEATURE SHAPE, SIZE AND LOCATION MAY VARY.

4. MAXIMUM SOLDER BALL DIAMETER MEASURED PARALLEL TO DATUM C.

$\sqrt{5.}$  datum c, the seating plane, is determined by the spherical crowns of the solder balls.

6. THIS PACKAGE HAS A BACK SIDE COATING THICKNESS OF 0.025.

© NXP SEMICONDUCTORS N.V. ALL RIGHTS RESERVED

DATE: 14 MAR 2018

| MECHANICAL OUTLINE         | STANDARD: | DRAWING NUMBER: | REVISION: |  |

|----------------------------|-----------|-----------------|-----------|--|

| PRINT VERSION NOT TO SCALE | NON JEDEC | SOT1966-2       | 0         |  |

Fig. 2. Package outline note WLCSP81 (SOT1966-2)

WLCSP81, wafer level chip-scale package; 81 bumps; 0.35 mm pitch, 3.55 mm x 3.36 mm x 0.365 mm body (backside coating included)

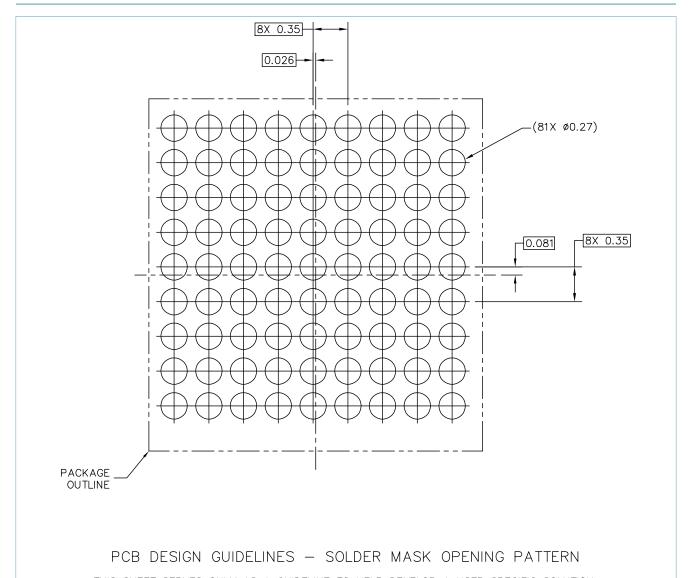

## 3. Soldering

THIS SHEET SERVES ONLY AS A GUIDELINE TO HELP DEVELOP A USER SPECIFIC SOLUTION. DEVELOPMENT EFFORT WILL STILL BE REQUIRED BY END USERS TO OPTIMIZE PCB MOUNTING PROCESSES AND BOARD DESIGN IN ORDER TO MEET INDIVIDUAL/SPECIFIC REQUIREMENTS.

| © NXP SEMICONDUCTORS N.V. ALL RIGHTS RESERVED |                            |           | DATE: 1         | 4 MAR 2018 |  |

|-----------------------------------------------|----------------------------|-----------|-----------------|------------|--|

|                                               | MECHANICAL OUTLINE         | STANDARD: | DRAWING NUMBER: | REVISION:  |  |

|                                               | PRINT VERSION NOT TO SCALE | NON JEDEC | SOT1966-2       | 0          |  |

**Reflow soldering footprint for SOT1966-2** Fig. 3.

SOT1966-2

**Package information** 6 April 2018

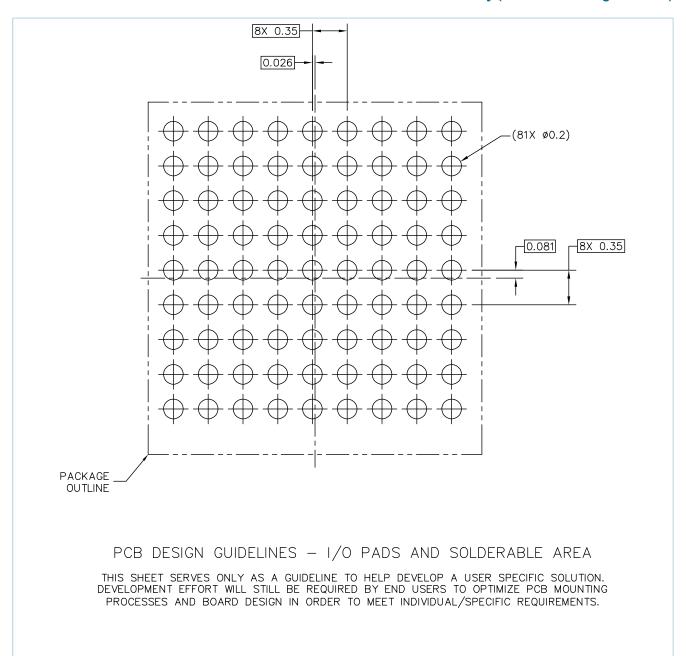

WLCSP81, wafer level chip-scale package; 81 bumps; 0.35 mm pitch, 3.55 mm x 3.36 mm x 0.365 mm body (backside coating included)

| © NXP SEMICONDUC           | TORS N.V. ALL RIGHTS RESE | ERVED           | DATE: 1   | 4 MAR 2018 |

|----------------------------|---------------------------|-----------------|-----------|------------|

| MECHANICAL OUTLINE         | STANDARD:                 | DRAWING NUMBER: | REVISION: |            |

| PRINT VERSION NOT TO SCALE | NON JEDEC                 | SOT1966-2       | 0         |            |

Fig. 4. Reflow soldering footprint part2 for WLCSP81 (SOT1966-2)

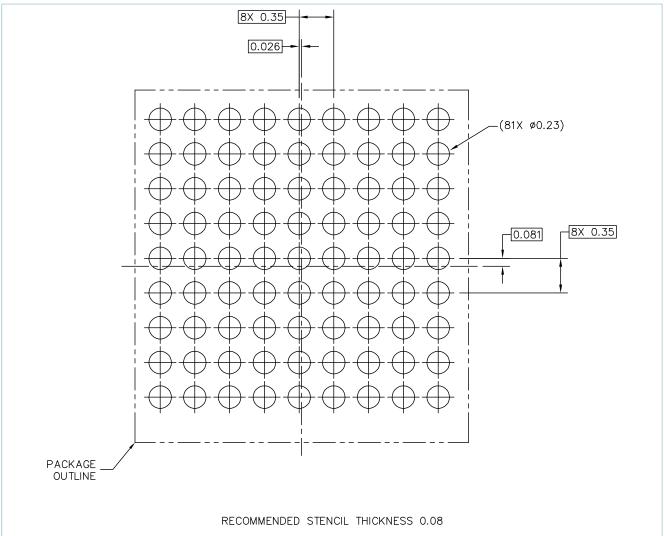

WLCSP81, wafer level chip-scale package; 81 bumps; 0.35 mm pitch, 3.55 mm x 3.36 mm x 0.365 mm body (backside coating included)

PCB DESIGN GUIDELINES - SOLDER PASTE STENCIL

THIS SHEET SERVES ONLY AS A GUIDELINE TO HELP DEVELOP A USER SPECIFIC SOLUTION. DEVELOPMENT EFFORT WILL STILL BE REQUIRED BY END USERS TO OPTIMIZE PCB MOUNTING PROCESSES AND BOARD DESIGN IN ORDER TO MEET INDIVIDUAL/SPECIFIC REQUIREMENTS.

| © NXP SEMICONDUCTORS N.V. ALL RIGHTS RESERVED |           |                 | DATE: 14  | 4 MAR 2018 |

|-----------------------------------------------|-----------|-----------------|-----------|------------|

| MECHANICAL OUTLINE                            | STANDARD: | DRAWING NUMBER: | REVISION: |            |

| PRINT VERSION NOT TO SCALE                    | NON JEDEC | SOT1966-2       | 0         |            |

Fig. 5. Reflow soldering footprint part3 for WLCSP81 (SOT1966-2)

WLCSP81, wafer level chip-scale package; 81 bumps; 0.35 mm pitch, 3.55 mm x 3.36 mm x 0.365 mm body (backside coating included)

### 4. Legal information

#### **Disclaimers**

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the *Terms and conditions of commercial sale* of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

WLCSP81, wafer level chip-scale package; 81 bumps; 0.35 mm pitch, 3.55 mm x 3.36 mm x 0.365 mm body (backside coating included)

### 5. Contents

| 1.  | Package summary                                                                                                                                             | . ' |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.  | Package outline                                                                                                                                             | . 2 |

| 3.  | Soldering                                                                                                                                                   | . 4 |

| 4.  | Legal information                                                                                                                                           | . 7 |

|     |                                                                                                                                                             |     |

| © N | XP B.V. 2018. All rights reserved                                                                                                                           | _   |

| For | more information, please visit: http://www.nxp.com<br>sales office addresses, please send an email to: salesaddresses@nxp.com<br>a of release: 6 April 2018 |     |