# **UM11406**

NTAG 5 I<sup>2</sup>C Cockpit application Rev. 1.1 — 13 August 2020 597411

**User manual COMPANY PUBLIC**

### **Document information**

| Information | Content                                                                                          |

|-------------|--------------------------------------------------------------------------------------------------|

| Keywords    | NTAG 5 link, NTAG 5 boost, I2C, reference application                                            |

| Abstract    | Description of NTAG 5 I2C Cockpit application allowing to configure NTAG 5 through I2C interface |

# NTAG 5 I<sup>2</sup>C Cockpit application

### **Revision history**

| Rev   | Date     | Description               |

|-------|----------|---------------------------|

| v.1.1 | 20200813 | Update of the application |

| v.1.0 | 20200511 | First version             |

NTAG 5 I<sup>2</sup>C Cockpit application

# 1 Abbreviations

### Table 1. Abbreviations

| Acronym          | Description                                 |

|------------------|---------------------------------------------|

| ALM              | Active Load Modulation                      |

| EH               | Energy Harvesting                           |

| ED               | Event Detection                             |

| GUI              | Graphical User Interface                    |

| I <sup>2</sup> C | Inter-Integrated Circuit                    |

| LED              | Light Emitting Diode                        |

| NFC              | Near Field Communication                    |

| RGB              | Red Green Blue                              |

| SLDA             | Software License and Distribution Agreement |

| USB              | Universal Serial Bus                        |

| VCOM             | Virtual COMmunication                       |

| μC               | micro-Controller                            |

NTAG 5 I<sup>2</sup>C Cockpit application

### 2 Introduction

This document describes NTAG 5 I<sup>2</sup>C Cockpit application allowing to configure NTAG 5 through [I<sup>2</sup>C interface].

The NTAG 5 I<sup>2</sup>C Cockpit application is a GUI application running on Windows platform, connected to NTAG 5 I<sup>2</sup>C interface via a "USB-I2C bridge".

The reference "USB-I2C bridge" implementation further presented in chapter <u>USB-I2C bridge</u> is based on LPC11U37H NXP's MCU and [NTAG 5 demoboard], but can also be ported to another environment using instructions provided in chapter <u>Porting to other hardware</u>.

Detailed description of the NTAG 5 Cockpit application can be found in chapter NTAG 5 I<sup>2</sup>C Cockpit GUI.

In case of issue running the application, one can find debugging information in related troubleshooting chapter <u>Troubleshooting</u>.

NTAG 5 I<sup>2</sup>C Cockpit application

# 3 Setup

### 3.1 Hardware setup

The hardware used to build the reference setup is the assembly of [LPC11U37H LPCXpresso board] acting as USB-I2C bridge, and [NTAG 5 development kit].

# 3.1.1 USB-I<sup>2</sup>C bridge

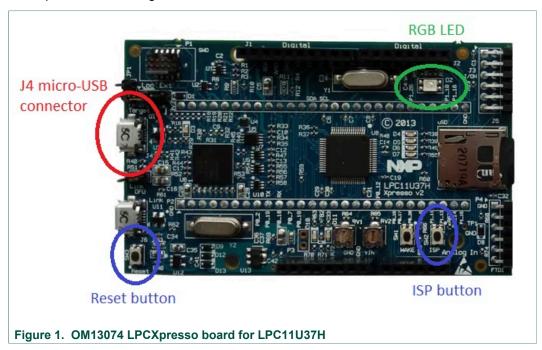

[OM13074 LPCXpresso board] featuring NXP LPC11U37H MCU is used as reference hardware to provide USB-I<sup>2</sup>C bridge. It allows offering an easy way to connect NTAG 5 to a computer and exchange over I<sup>2</sup>C interface.

Dedicated firmware built for this specific function is provided as part of the NTAG 5 I<sup>2</sup>C Cockpit release.

Flashing the OM13074 board is then simply done following below sequence:

- Connect computer's USB port to J4 OM13074 Micro-USB connector using USB cable (USB male Type A to micro-USB)

- Put the board in flash mode by keeping ISP button pulled while resetting the board (pressing Reset button)

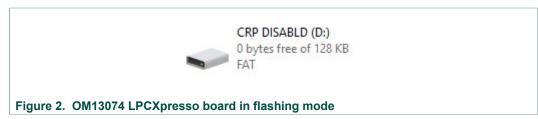

- The board should be mounted as "mass-storage" device on the computer and seen under name "CRP DISABLD" in Windows Explorer:

© NXP B.V. 2020. All rights reserved.

User manual

**COMPANY PUBLIC**

### NTAG 5 I<sup>2</sup>C Cockpit application

- Browse to the related device folder ("D:" in the above example), only one single file named "firmware.bin" should be present

- Delete the "firmware.bin" file

- Copy "USB-I2C bridge LPC11u37h.bin" file from NTAG 5 I<sup>2</sup>C Cockpit installation folder to the device folder ("D:" in the above example)

- Reset the OM13074 board, pressing Reset Button or unplugging/plugging the USB cable

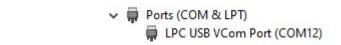

- The RGB LED should go RED then GREEN and the board should appear as Virtual COM port under Windows Device Manager:

Figure 3. USB-I2C bridge board for LPC11U37H in Device Manager

In case of issue observed during this procedure, please refer to the related troubleshooting chapter Troubleshooting.

### 3.1.2 NTAG 5 board

Either on of the two versions of [NTAG 5 development kit] ("OM2NTP5332 NTAG 5 link/ switch development kit" and "OM2NTA5332 NTAG 5 boost development kit") can be used as reference setup.

Figure 4. OM2NTP5332: NTAG 5 link/switch development kit

### NTAG 5 I<sup>2</sup>C Cockpit application

Make sure NTAG 5 is properly set in "I2C use case mode" (which is release default state of the OM2NTx5332 boards) to enable NTAG 5 I<sup>2</sup>C interface. For further information refer to the troubleshooting chapter Troubleshooting.

Simply assemble OM2NTx5332 board to the Arduino header of OM13074 board. Then plug OM13074 board to computer's USB port (as described in chapter Section 3.1.1), OM2NTx5332 board's LED referenced as "D1" should light on. If not, please refer to the troubleshooting chapter **Troubleshooting**

### 3.2 Software setup

Installation of the tool is done running NTAG 5 Cockpit installer which can be downloaded from NTAG 5 development kit webpage (OM2NTx5332). NTAG 5 Cockpit installer includes both NTAG 5 I<sup>2</sup>C Cockpit application and NTAG 5 NFC Cockpit application (see UM11207 for more details).

The installer creates an NTAG5 Cockpit folder (by default under "C:\nxp\" directory) containing:

- NTAG 5 I<sup>2</sup>C Cockpit application executable

- USB-I2C bridge firmware binary for NXP LPC11U37H MCU

- a link to the present document on NXP website

- NXP Infrastructure SLDA licensing terms

- · related Software Content Register detailing components license details

- NTAG 5 NFC Cockpit application executable

- · an executable allowing to uninstall the current package

UM11406

### NTAG 5 I<sup>2</sup>C Cockpit application

The installer also allows creating related folder containing shortcuts in Windows Start Menu, as well as NTAG 5 Cockpit application shortcuts on Windows Desktop.

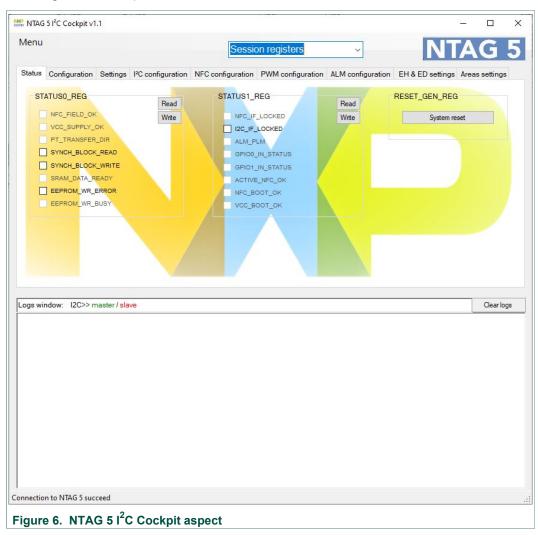

Running the NTAG 5 I<sup>2</sup>C Cockpit application executable, considering reference setup depicted in chapter <u>Hardware setup</u> is connected to the computer, shall trigger the following window to open:

If not, please refer to the troubleshooting chapter <u>Troubleshooting</u>.

NTAG 5 I<sup>2</sup>C Cockpit application

# 4 NTAG 5 I<sup>2</sup>C Cockpit GUI

The purpose of the current chapter is to describe the NTAG 5 I<sup>2</sup>C Cockpit tool in details.

### 4.1 Register selection

The "Register selection" item allows defining which register bank applies to the "Tabs" items.

Indeed NTAG 5 registers are split between "Configuration registers" (from 1000h to 109Fh in Configuration memory) and "Session registers" (from 10A0h to 10AFh in Configuration memory).

Pay attention that "Session registers" settings apply to the current session (apply as soon as set) while "Configuration registers" settings only apply to the next session (apply after Power On Reset).

### 4.2 Tabs

"Tabs" items exposes NTAG 5 registers definition allowing to set and get NTAG 5 IC configuration. Detailed registers definition is given in NTAG 5 data sheet for reference.

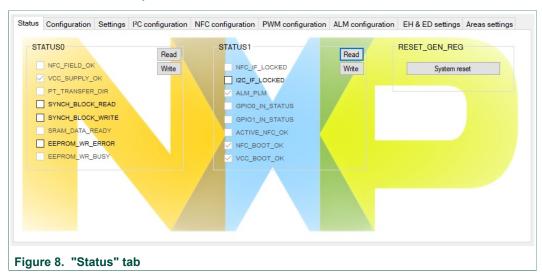

### **4.2.1 Status**

"Status" tab is only valid for "Session registers" since the related registers are only defined for this memory area.

### NTAG 5 I<sup>2</sup>C Cockpit application

STATUS0 and STATUS1 registers writeable bits (not grayed ones) can only be written to 0, clearing the related information.

"System reset" button performs software reset of the NTAG 5 IC, thus allowing current configuration settings being loaded to a new session.

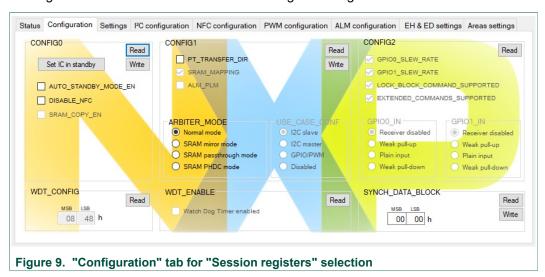

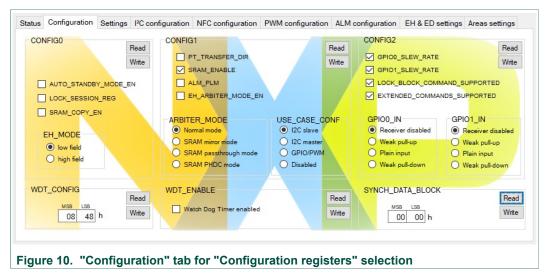

### 4.2.2 Configuration

"Configuration" tab has different looks according to the register selection.

"Set IC in standby" button triggers NTAG 5 IC entering in standby mode. Pay attention that next I<sup>2</sup>C request will woken-up the NTAG 5 IC thus this first request will fail because not acknowledged by NTAG 5 IC.

"ARBITER\_MODE" setting from "CONFIG1 register" can only be set if "SRAM\_MAPPING" is enabled. Enabling "SRAM\_MAPPING is done setting "SRAM ENABLE" bit is set in "CONFIG1" register within "Configuration register" area.

Pay attention that changing "USE\_CASE\_CONFIG" setting from "CONFIG1" register will impact NTAG 5 I<sup>2</sup>C settings and may prevent (is set to other than "I2C slave") to drive

### NTAG 5 I<sup>2</sup>C Cockpit application

it from NTAG 5 I<sup>2</sup>C Cockpit anymore until this setting is reset back to "I2C slave" (only possibility is then via NFC interface).

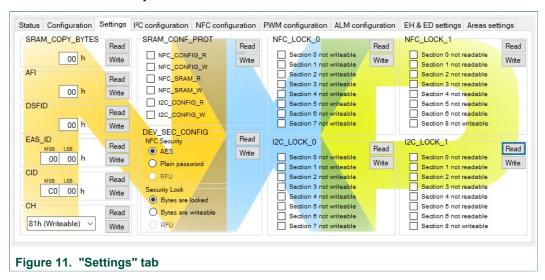

### 4.2.3 Settings

"Settings" tab is only valid for "Configuration registers" since the related registers are only defined for this memory area.

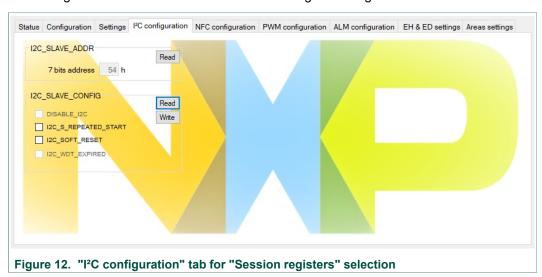

### 4.2.4 I<sup>2</sup>C configuration

"I2C configuration" tab has different looks according to the register selection.

### NTAG 5 I<sup>2</sup>C Cockpit application

Figure 13. "I2C configuration" tab for "Configuration registers" selection

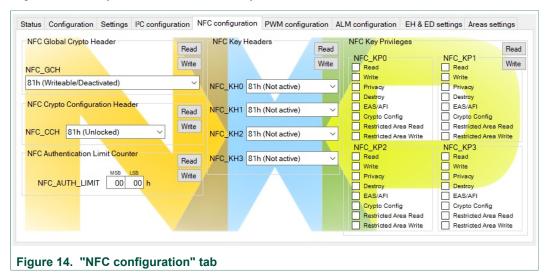

### 4.2.5 NFC configuration

"NFC configuration" tab is only valid for "Configuration registers" since the related registers are only defined for this memory area.

"NFC Key Headers" and "NFC Key Privileges" settings can only set if NFC Security is enabled. "NFC Security" setting is set through "DEV\_SEC\_CONFIG" register (see "Settings" tab).

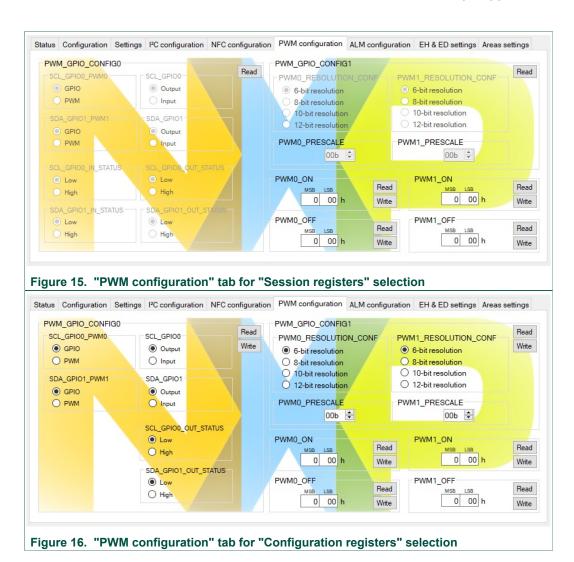

### 4.2.6 PWM configuration

"PWM configuration" tab has different looks according to the register selection.

# NTAG 5 I<sup>2</sup>C Cockpit application

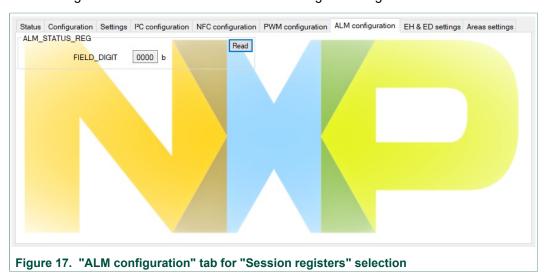

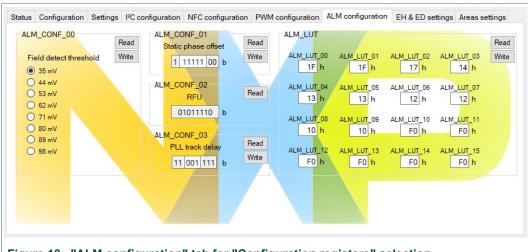

### 4.2.7 ALM configuration

"ALM configuration" tab has different looks according to the register selection.

UM11406

### NTAG 5 I<sup>2</sup>C Cockpit application

Figure 18. "ALM configuration" tab for "Configuration registers" selection

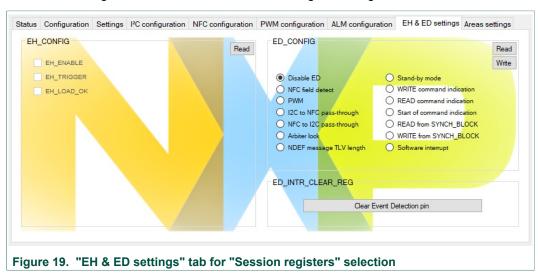

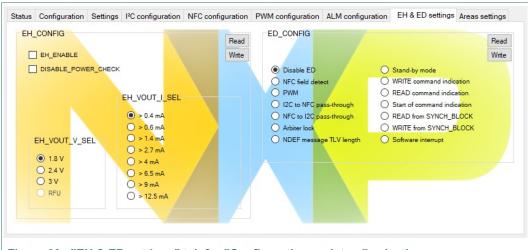

### 4.2.8 EH & ED settings

"EH & ED settings" tab has different looks according to the register selection.

<sup>&</sup>quot;Clear Event Detection pin" button trigger clearing the detection pin.

# NTAG 5 I<sup>2</sup>C Cockpit application

Figure 20. "EH & ED settings" tab for "Configuration registers" selection

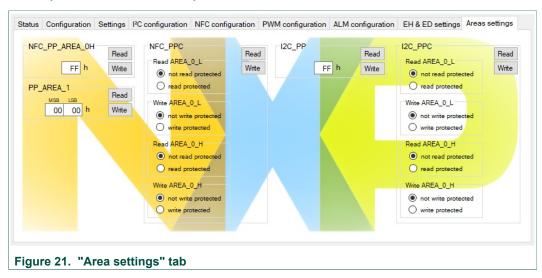

### 4.2.9 Area settings

"Area settings" tab is only valid for "Configuration registers" since the related registers are only defined for this memory area.

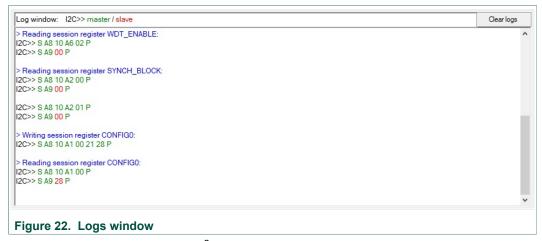

### 4.3 Logs window

Bottom area of the NTAG 5 I<sup>2</sup>C Cockpit tool displays logs:

- · In blue: operation details

- In Black: status

- In Green: I<sup>2</sup>C master data (to NTAG 5), 'S' indicating start condition while 'P' indicates stop condition

- In Red: I<sup>2</sup>C slave data (from NTAG 5), 'S' indicating start condition while 'P' indicates stop condition

# NTAG 5 I<sup>2</sup>C Cockpit application

More detailed information about I<sup>2</sup>C interface is given in NTAG 5 data sheet.

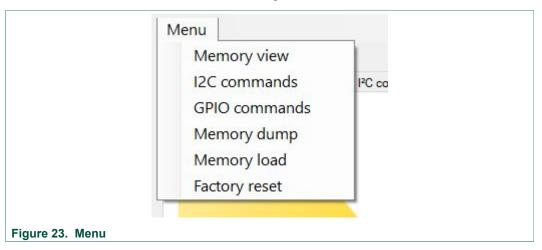

### 4.4 Menu

Additional functionalities are accessible through "Menu" item.

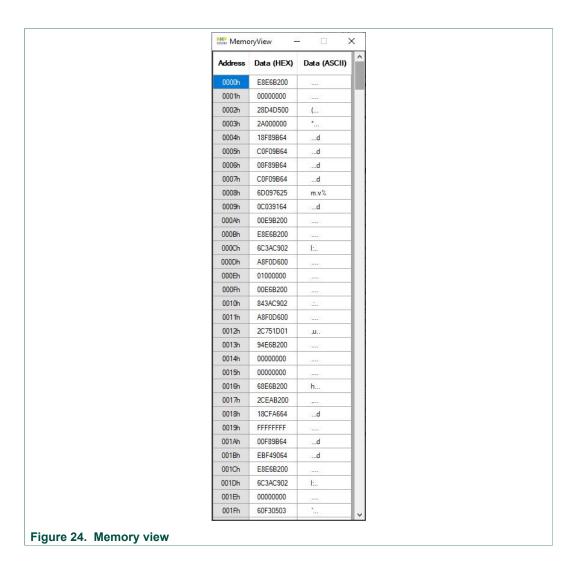

### 4.4.1 Memory view

"Memory view" allows displaying and updating NTAG 5 memory. Values are refreshed while scrolling.

# NTAG 5 I<sup>2</sup>C Cockpit application

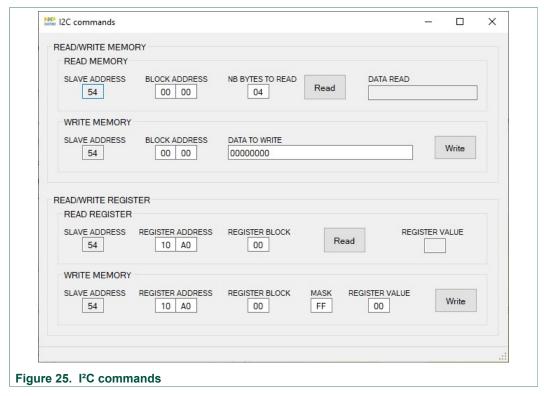

### 4.4.2 I<sup>2</sup>C commands

"I²C commands" offers possibility to perform read or write memory operations as well as read or write register.

# NTAG 5 I<sup>2</sup>C Cockpit application

"READ/WRITE REGISTER" operations are reserved to "Session registers" (from 10A0h to 10AFh in Configuration memory). Reading or writing "Configuration registers" (from 1000h to 109Fh in Configuration memory) must be done via "READ/WRITE MEMORY" operations.

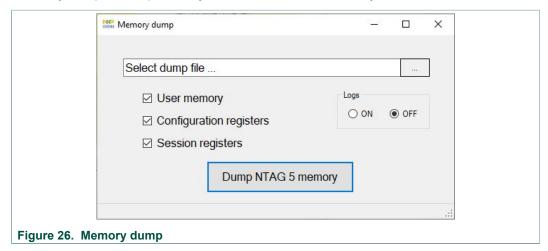

### 4.4.3 Memory dump

"Memory dump" offers possibility to read out NTAG 5 memory and store it to a file.

Output file content looks like this:

### NTAG 5 I<sup>2</sup>C Cockpit application

```

Ntag5 memory dump from 2020-04-28-12:12

User memory:

0000h : FF FF FF FF

0001h : FF FF FF FF

0002h : FF FF FF FF

0003h : FF FF FF FF

0004h : FF FF FF FF

01FEh : FF FF FF FF

Configuration registers:

1000h : 00 00 00 00

1001h : 00 00 00 00

1002h : 00 00 00 00

1003h : 00 00 00 00

1004h : 00 00 00 00

1099h : 00 00 00 00

Session registers:

10A0h : 02 C4 00 00

10A1h : 08 02 0F 00

10A2h : 00 00 00 00

10A3h : 00 00 00 00

10A4h : 00 00 00 00

10A5h : 00 00 00 00

10A6h : 48 08 00 00

10A7h : 00 00 00 00

10A8h : 00 00 00 00

10A9h : 54 00 00 00

10AAh : 00 00 00 00

10ABh : 00 00 00 00

10ACh : 00 00 04 00

10ADh : 00 00 00 00

Figure 27. Memory dump output file content

```

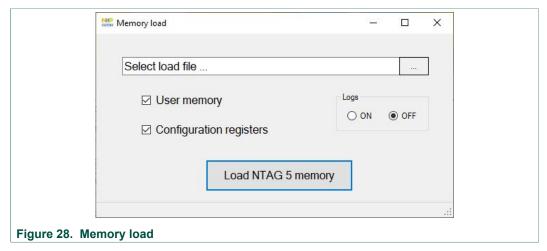

### 4.4.4 Memory load

"Memory load" offers possibility to load NTAG 5 memory from data contained in a file.

The input file must be formatted following below definition for each line (one memory block of 4 bytes per line):

# NTAG 5 I<sup>2</sup>C Cockpit application

${ t VVVVh}$ : WW XX YY ZZ where VVVVh is the memory block base address (in hexadecimal) and WW XX YY ZZ respective values (in hexadecimal) of the memory block.

For example: 1041h: 1F 1F 17 14 triggers writing values 0x1F1F1714 at memory address 1041h (settings ALM\_LUT\_00, ALM\_LUT\_01, ALM\_LUT\_02 and ALM\_LUT\_03).

File obtained from "Memory dump" operation (see "Memory dump") can be used as input to "Memory load" operation.

It is not possible to load content to "Session registers" area (from 10A0h to 10AFh in Configuration memory) via "Memory Load" operation.

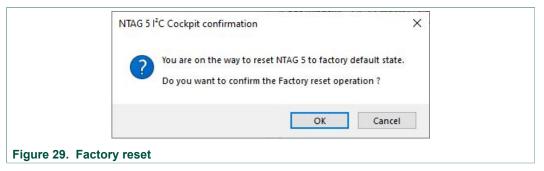

### 4.4.5 Factory reset

"Factory reset" allows applying default configuration to NTAG 5.

The default configuration is only applied after confirmation from user.

Pay attention that this is done considering the limitation of register access rights (according to the current configuration some registers may not be writeable).

NTAG 5 I<sup>2</sup>C Cockpit application

# 5 Porting to other hardware

### 5.1 Other USB-I2C bridge

NTAG 5 I<sup>2</sup>C Cockpit tool can be used with another setup than the one described in chapter <u>Hardware setup</u>. It requires porting USB-I2C bridge implementation to this different environment.

The NTAG 5 I<sup>2</sup>C Cockpit tool interfaces to USB-I2C bridge via VCOM port. The related USB Device instance path shall contain "USB\VID\_1FC9&PID\_0083" string.

Frame interface definition is then defined as described in below table:

Table 2. NTAG 5 I<sup>2</sup>C Cockpit to USB-I2C bridge frame definition

| Frame size | I <sup>2</sup> C address<br>(7 bits) | Nb bytes<br>to write (N) | Bytes to write | Nb bytes<br>to read (M) |

|------------|--------------------------------------|--------------------------|----------------|-------------------------|

| 1 byte     | 1 byte                               | 1 byte                   | N bytes        | 1 byte                  |

Table 3. USB-I2C bridge to NTAG 5 I<sup>2</sup>C Cockpit frame definition

| Frame size | Status | Bytes read |

|------------|--------|------------|

| 1 byte     | 1 byte | M bytes    |

Table 4. USB-I2C bridge to NTAG 5 I<sup>2</sup>C Cockpit frame status definition

| Status value | Status information                   |

|--------------|--------------------------------------|

| 0x00         | Success                              |

| 0x01         | USB communication error              |

| 0x02         | I <sup>2</sup> C address error       |

| 0x03         | I <sup>2</sup> C communication error |

The USB-I2C bridge interface also offers possibility to drive MCU GPIO, purpose is providing access to ED and HPD pin functionality.

Frame interface definition is similar to I<sup>2</sup>C communication, except that 2<sup>nd</sup> byte (7 bits I<sup>2</sup>C address byte) must be set to FFh:

Table 5. NTAG 5 I<sup>2</sup>C Cockpit to USB-I2C bridge frame definition for GPIO access

| Frame size | 0xFF   | Port Nb | Pin Nb | Direction<br>(0 = input,<br>1 = output) | Pin state<br>(only if<br>output)                     |

|------------|--------|---------|--------|-----------------------------------------|------------------------------------------------------|

| 1 byte     | 1 byte | 1 byte  | 1 byte | 1 byte                                  | 1 byte (if<br>Direction<br>is output,<br>else empty) |

Table 6. USB-I2C bridge to NTAG 5 I<sup>2</sup>C Cockpit frame definition for GPIO access

| Frame size | Status | Pin state (only if input)                  |

|------------|--------|--------------------------------------------|

| 1 byte     | 1 byte | 1 byte (if Direction is input, else empty) |

UM11406

# NTAG 5 I<sup>2</sup>C Cockpit application

Table 7. USB-I2C bridge to NTAG 5 I<sup>2</sup>C Cockpit frame status definition for GPIO access

| Status value | Status information      |

|--------------|-------------------------|

| 0x00         | Success                 |

| 0x01         | USB communication error |

The reference implementation of this USB-I2C bridge on NXP's MCU LPC11U37H is provided as part of [SW6090] delivery available from [NTAG 5 development kit] webpage.

### 5.2 Other NTAG 5 board

It is possible to reuse USB-I2C bridge detailed in chapter <u>Section 3.1.1</u> to drive NTAG 5 IC from another board than NTAG 5 demo kit depicted in chapter <u>Section 3.1.2</u>.

To do this, following connections between [OM13074 LPCXpresso board] and NTAG 5 IC must be insured:

Table 8. NTAG 5 connections to USB-I2C bridge

| Signal          | OM13074 LPCXpresso board                                                   | NTAG 5 IC pins |

|-----------------|----------------------------------------------------------------------------|----------------|

| I2C_SCL         | Arduino connector J1 pin #1                                                | SCL pin #7     |

| I2C_SDA         | Arduino connector J1 pin #2                                                | SDA pin #6     |

| Power supply    | Arduino connector J7 pin #4 (+3.3 V) or Arduino connector J7 pin #5 (+5 V) | VCC pin #9     |

| Event detection | Arduino connector J2 pin #5                                                | ED pin #8      |

| Hard Power Down | Arduino connector J2 pin #6                                                | HPD pin #10    |

| Ground          | Arduino connector J7 pin #6 or #7 or Arduino connector J1 pin #4           | GND pin #1     |

NTAG 5 I<sup>2</sup>C Cockpit application

# 6 Troubleshooting

### 6.1 Not able to flash OM13074 LPCXpresso board

In case of issue during flashing of USB-I2C bridge firmware to OM13074 LPCXpresso board, refer to the support information in [OM13074 LPCXpresso board].

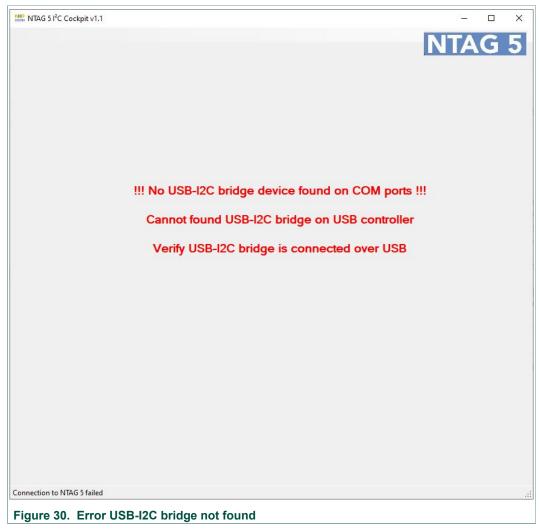

### 6.2 USB-I2C bridge not found

While starting NTAG 5 I<sup>2</sup>C Cockpit tool, in case following issue appears:

If [OM13074 LPCXpresso board] RGB LED is not lighted GREEN, it indicates USB-I2C bridge is not properly detected by the USB controller device:

- Make sure SW6 switch on [OM2NTx5332 board] is set to either "1.8\_3.3V" or "5V" selection (by default boards are delivered with SW6 switch kept in the "middle" selection)

- In case of OM2NTA5332 board, make sure SW7 switch is set to "Arduino supply" selection (position "1-3")

UM11406

NTAG 5 I<sup>2</sup>C Cockpit application

• refer to chapter <u>USB-I2C bridge</u> to reflash the [OM13074 LPCXpresso board]

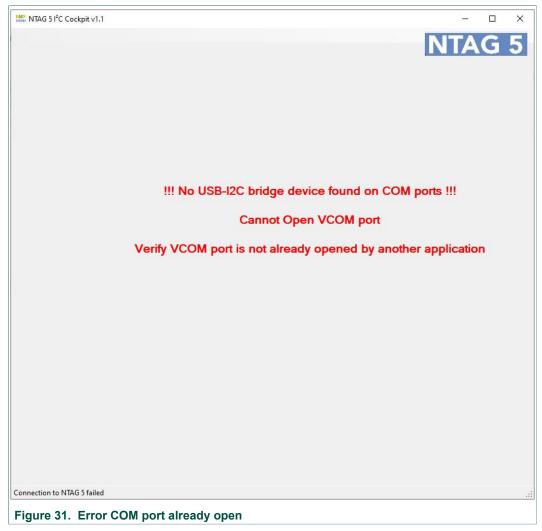

### 6.3 Virtual COM port already open

While starting NTAG 5 I<sup>2</sup>C Cockpit tool, in case following issue appears:

It indicates that USB-I2C bridge board has been detected on USB but related Virtual COM port is already open:

- Verify that no other instance of NTAG 5 I<sup>2</sup>C Cockpit is running

- Check that no other application has an open channel to the USB-I2C bridge-related COM port.

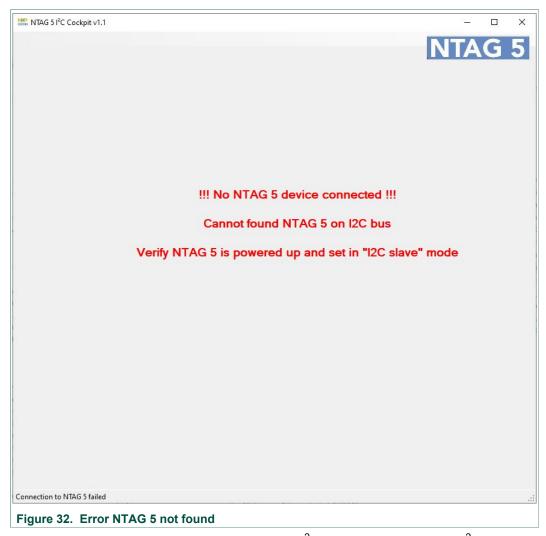

### 6.4 NTAG 5 not found

While starting NTAG 5 I<sup>2</sup>C Cockpit tool, in case following issue appears:

NTAG 5 I<sup>2</sup>C Cockpit application

It indicates NTAG 5 is not properly answering on I<sup>2</sup>C interface, whatever the I<sup>2</sup>C slave address (NTAG 5 I<sup>2</sup>C Cockpit tool scans all possible address from 0h to 7Fh):

- Verify that NTAG 5 IC is properly configured in I<sup>2</sup>C slave mode (refer to "USE\_CASE\_CONF" field of "CONFIG\_1" NTAG 5 configuration byte)

- Check that NTAG 5 is properly supplied (verify [OM2NTx5332 board] switches setting)

### 6.5 Any other issue

For any other issue, refer to [NFC support].

# NTAG 5 I<sup>2</sup>C Cockpit application

### 7 References

- [1] UM10204 I2C-bus specification and user manual https://www.nxp.com/docs/en/user-guide/UM10204.pdf

- [2] OM13074: LPCXpresso board for LPC11U37H https://www.nxp.com/products/security-and-authentication/authentication/lpcxpresso-board-for-lpc11u37h:OM13074

- [3] OM2NTx5332: NTAG® 5 development kits https://www.nxp.com/products/rfid-nfc/nfc-hf/ntag/nfc-tags-for-electronics/om2ntx5332-ntag-5-development-kits:OM2NTX5332

- [4] SW6090: NTAG 5 Development kit source code and library for LPC microcontrollers <a href="https://www.nxp.com/doc/SW6090">https://www.nxp.com/doc/SW6090</a>

- [5] NFC support in NXP community forum https://community.nxp.com/community/identification-security/nfc?tid=community

- [6] UM11207 NTAG 5 NFC Cockpit application https://www.nxp.com/docs/en/user-guide/UM11207.pdf

### NTAG 5 I<sup>2</sup>C Cockpit application

# 8 Legal information

### 8.1 Definitions

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

#### 8.2 Disclaimers

Limited warranty and liability - Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors. In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory. Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

Applications — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification. Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products. NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by

customer's third party customer(s). NXP does not accept any liability in this respect.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Evaluation products — This product is provided on an "as is" and "with all faults" basis for evaluation purposes only. NXP Semiconductors, its affiliates and their suppliers expressly disclaim all warranties, whether express, implied or statutory, including but not limited to the implied warranties of non-infringement, merchantability and fitness for a particular purpose. The entire risk as to the quality, or arising out of the use or performance, of this product remains with customer. In no event shall NXP Semiconductors, its affiliates or their suppliers be liable to customer for any special, indirect, consequential, punitive or incidental damages (including without limitation damages for loss of business, business interruption, loss of use, loss of data or information, and the like) arising out the use of or inability to use the product, whether or not based on tort (including negligence), strict liability, breach of contract, breach of warranty or any other theory, even if advised of the possibility of such damages. Notwithstanding any damages that customer might incur for any reason whatsoever (including without limitation, all damages referenced above and all direct or general damages), the entire liability of NXP Semiconductors, its affiliates and their suppliers and customer's exclusive remedy for all of the foregoing shall be limited to actual damages incurred by customer based on reasonable reliance up to the greater of the amount actually paid by customer for the product or five dollars (US\$5.00). The foregoing limitations, exclusions and disclaimers shall apply to the maximum extent permitted by applicable law, even if any remedy fails of its essential purpose.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security — While NXP Semiconductors has implemented advanced security features, all products may be subject to unidentified vulnerabilities. Customers are responsible for the design and operation of their applications and products to reduce the effect of these vulnerabilities on customer's applications and products, and NXP Semiconductors accepts no liability for any vulnerability that is discovered. Customers should implement appropriate design and operating safeguards to minimize the risks associated with their applications and products.

#### 8.3 Licenses

#### Purchase of NXP ICs with NFC technology

Purchase of an NXP Semiconductors IC that complies with one of the Near Field Communication (NFC) standards ISO/IEC 18092 and ISO/IEC 21481 does not convey an implied license under any patent right infringed by implementation of any of those standards. Purchase of NXP Semiconductors IC does not include a license to any NXP patent (or other IP right) covering combinations of those products with other products, whether hardware or software.

### 8.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

I<sup>2</sup>C-bus — logo is a trademark of NXP B.V.

$\ensuremath{\mathsf{NTAG}}$  — is a trademark of NXP B.V.

NXP — wordmark and logo are trademarks of NXP B.V.

UM11406

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2020. All rights reserved

# NTAG 5 I<sup>2</sup>C Cockpit application

# **Tables**

|         | Abbreviations3                       | Tab. 5. | NTAG 5 I2C Cockpit to USB-I2C bridge    |    |

|---------|--------------------------------------|---------|-----------------------------------------|----|

| Tab. 2. | NTAG 5 I2C Cockpit to USB-I2C bridge |         | frame definition for GPIO access        | 21 |

|         | frame definition21                   | Tab. 6. | USB-I2C bridge to NTAG 5 I2C Cockpit    |    |

| Tab. 3. | USB-I2C bridge to NTAG 5 I2C Cockpit |         | frame definition for GPIO access        | 21 |

|         | frame definition21                   | Tab. 7. | USB-I2C bridge to NTAG 5 I2C Cockpit    |    |

| Tab. 4. | USB-I2C bridge to NTAG 5 I2C Cockpit |         | frame status definition for GPIO access | 22 |

|         | frame status definition21            | Tab. 8. | NTAG 5 connections to USB-I2C bridge    | 22 |

# NTAG 5 I<sup>2</sup>C Cockpit application

# **Figures**

| Fig. 1.  | OM13074 LPCXpresso board for LPC11U37H5                 | Fig. 15. | "PWM configuration" tab for "Session registers" selection       | 13 |

|----------|---------------------------------------------------------|----------|-----------------------------------------------------------------|----|

| Fig. 2.  | OM13074 LPCXpresso board in flashing mode               | Fig. 16. | "PWM configuration" tab for "Configuration registers" selection |    |

| Fig. 3.  | USB-I2C bridge board for LPC11U37H in Device Manager6   | Fig. 17. | "ALM configuration" tab for "Session registers" selection       |    |

| Fig. 4.  | OM2NTP5332: NTAG 5 link/switch development kit          | Fig. 18. | "ALM configuration" tab for "Configuration registers" selection |    |

| Fig. 5.  | OM2NTA5332: NTAG 5 boost development kit7               | Fig. 19. | "EH & ED settings" tab for "Session registers" selection        |    |

| Fig. 6.  | NTAG 5 I2C Cockpit aspect8                              | Fig. 20. | "EH & ED settings" tab for "Configuration                       |    |

| Fig. 7.  | Register selection9                                     |          | registers" selection                                            | 15 |

| Fig. 8.  | "Status" tab9                                           | Fig. 21. | "Area settings" tab                                             | 15 |

| Fig. 9.  | "Configuration" tab for "Session registers"             | Fig. 22. | Logs window                                                     | 16 |

|          | selection10                                             | Fig. 23. | Menu                                                            | 16 |

| Fig. 10. | "Configuration" tab for "Configuration                  | Fig. 24. | Memory view                                                     | 17 |

|          | registers" selection10                                  | Fig. 25. | I <sup>2</sup> C commands                                       |    |

| Fig. 11. | "Settings" tab11                                        | Fig. 26. | Memory dump                                                     | 18 |

| Fig. 12. | "I <sup>2</sup> C configuration" tab for "Session       | Fig. 27. | Memory dump output file content                                 | 19 |

|          | registers" selection11                                  | Fig. 28. | Memory load                                                     | 19 |

| Fig. 13. | "I <sup>2</sup> C configuration" tab for "Configuration | Fig. 29. | Factory reset                                                   | 20 |

| -        | registers" selection12                                  | Fig. 30. | Error USB-I2C bridge not found                                  | 23 |

| Fig. 14. | "NFC configuration" tab12                               | Fig. 31. | Error COM port already open                                     |    |

| -        | -                                                       | Fig. 32. | Error NTAG 5 not found                                          |    |

|          |                                                         |          |                                                                 |    |

# NTAG 5 I<sup>2</sup>C Cockpit application

### **Contents**

| 1     | Abbreviations                        | 3  |

|-------|--------------------------------------|----|

| 2     | Introduction                         | 4  |

| 3     | Setup                                |    |

| 3.1   | Hardware setup                       |    |

| 3.1.1 | USB-I2C bridge                       | 5  |

| 3.1.2 | NTAG 5 board                         | 6  |

| 3.2   | Software setup                       | 7  |

| 4     | NTAG 5 I2C Cockpit GUI               | 9  |

| 4.1   | Register selection                   | 9  |

| 4.2   | Tabs                                 | 9  |

| 4.2.1 | Status                               | 9  |

| 4.2.2 | Configuration                        | 10 |

| 4.2.3 | Settings                             | 11 |

| 4.2.4 | I <sup>2</sup> C configuration       | 11 |

| 4.2.5 | NFC configuration                    | 12 |

| 4.2.6 | PWM configuration                    | 12 |

| 4.2.7 | ALM configuration                    | 13 |

| 4.2.8 | EH & ED settings                     |    |

| 4.2.9 | Area settings                        | 15 |

| 4.3   | Logs window                          | 15 |

| 4.4   | Menu                                 | 16 |

| 4.4.1 | Memory view                          | 16 |

| 4.4.2 | I <sup>2</sup> C commands            | 17 |

| 4.4.3 | Memory dump                          | 18 |

| 4.4.4 | Memory load                          | 19 |

| 4.4.5 | Factory reset                        | 20 |

| 5     | Porting to other hardware            | 21 |

| 5.1   | Other USB-I2C bridge                 | 21 |

| 5.2   | Other NTAG 5 board                   |    |

| 6     | Troubleshooting                      |    |

| 6.1   | Not able to flash OM13074 LPCXpresso |    |

|       | board                                | 23 |

| 6.2   | USB-I2C bridge not found             | 23 |

| 6.3   | Virtual COM port already open        |    |

| 6.4   | NTAG 5 not found                     |    |

| 6.5   | Any other issue                      | 25 |

| 7     | References                           |    |

| 8     | Legal information                    | 27 |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.