お客様の素早い設計とより早い製品化を実現する、技術情報と専門知識をご紹介します。

CBTU02044は、サーバおよびクライアント・アプリケーションでのPCIe4.0とのインターフェース用に最適化された高速差動1対2スイッチング・チップです。この高性能スイッチ・チップは、PCIe-Gen4、MIPI、DP1.4、DDRなど他の高速インターフェースにも使用できます。

さらに、CBTU02044は、2つの差動ポート(ポートBまたはC)の出力として1つ(ポートA)を選択することで、2対1のマルチプレクサとしても機能します。ピン配置は、レイアウトの層数が最小限となるよう最適化され、高いデータ・レートでの厳格なクロストーク仕様を満たす非常に低いクロストークを実現しています。

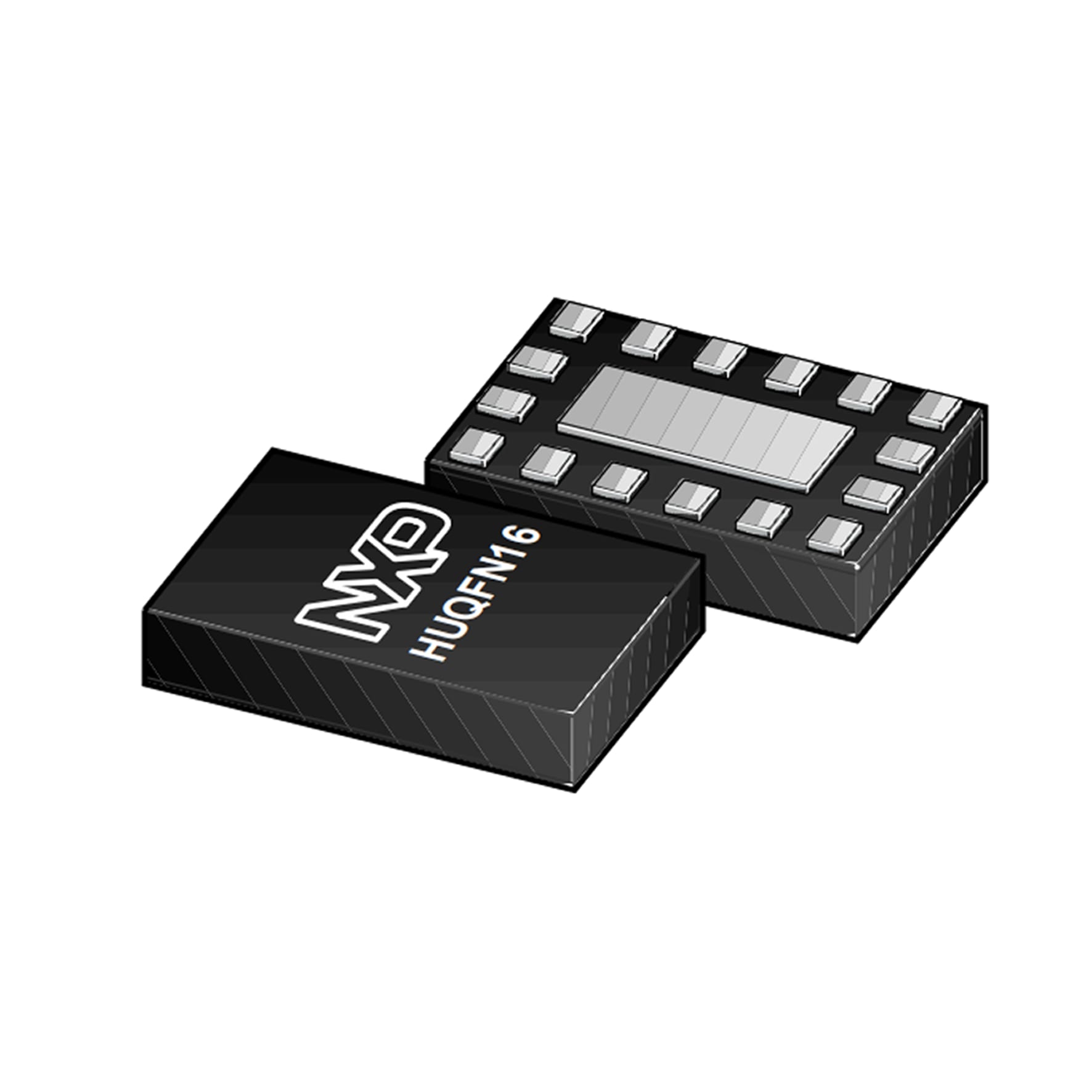

CBTU02044は、占有面積を削減するためにフットプリントが最適化された小型パッケージです。0.4 mmピッチの1.6 mm x 2.4 mm x 0.5 mm HUQFN16パッケージで提供されます。

|

|

|

|

|

|

|

|---|---|---|---|---|---|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

クイック・リファレンス ドキュメンテーションの種類

3 ドキュメント

コンパクトリスト

セキュアファイルの読み込み中、しばらくお待ちください。