OM13561

アクティブ

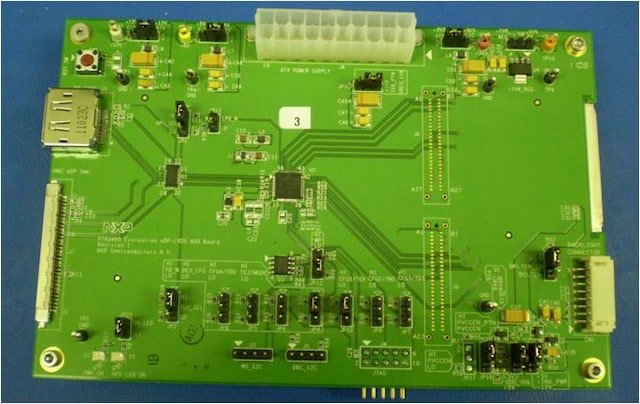

PTN3460I demo board.

キットの内容

Kit Contains:

- Demo Board

- Setup instruction

- Schematic pages