Author

Ghoshank Patel

Ghoshank Patel is a product marketer for NXP Network Edge Processing Group. He holds a Bachelor of Science in Electrical and Computer Engineering from the University of Texas at Austin.

As recently as 10 years ago, system vendors commonly used multiple instruction sets including Power, MIPs, Arm and x86. With too many options the edge ecosystem was disjointed and it became difficult to develop standard software that was compliant with a wide range of hardware. This led to vertical solutions where a single vendor would provide a variety of proprietary hardware and software that was compatible with each other as long as customers didn’t introduce anything from another vendor. Customers had little leverage in such a case and solutions were expensive.

Since the middle of the last decade, the industry has consolidated around two instruction sets, Arm and x86. While the x86 ecosystem is currently dominated by Intel, the Arm ecosystem has both the advantage and disadvantage of having many members in it. The advantage is healthy competition between vendors which leads to more innovation, specialization, and optimization for certain use cases, and lower costs. Additionally, the Arm consolidation happened specifically around the Arm v8 64b architecture, so the software binaries could run across silicon from all vendors. The DPDK application programming interface makes it possible to have a standard interface towards the hardware from a Linux user-space application. So once the user has Linux running, everything above it looks homogenous. However, this leads to the downside of a vibrant ecosystem – getting Linux running on an SOC could still be a fairly vendor-specific thing. Despite support from the standard bootloader, there is still enough variance between silicon and software from different vendors that it becomes a difficult porting task for the OS vendor.

Arm’s Project Cassini is an initiative to accelerate the deployment of cloud native applications across diverse Arm platforms. It enables the Linux ecosystem vendors to easily work across many Arm platforms by creating standards and testing regimes that ensure this homogeneity.

-Ghoshank Patel

Arm’s Project Cassini is an initiative to accelerate the deployment of cloud native applications across diverse Arm platforms. It enables the Linux ecosystem vendors to easily work across many Arm platforms by creating standards and testing regimes that ensure this homogeneity. One of the pillars of Project Cassini is called Arm SystemReady—a set of standards and a compliance certification program that enables interoperability with standard, off-the-shelf operating systems and hypervisors.

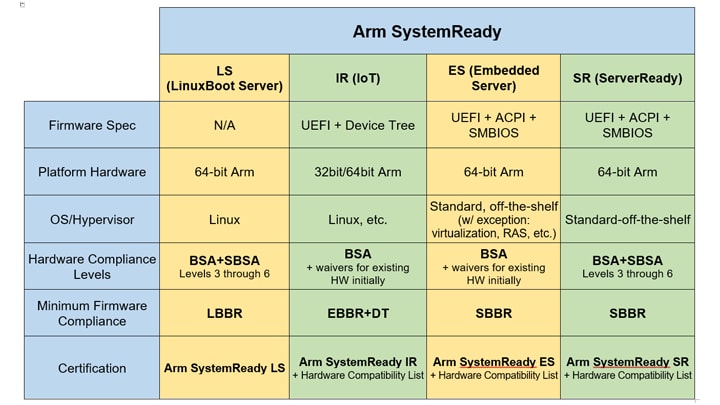

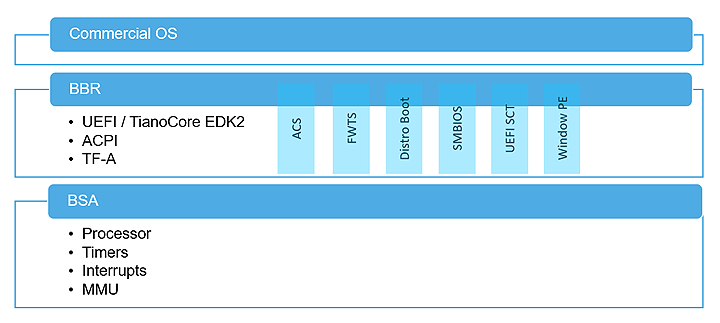

Project Cassini defines four bands to their SystemReady designation. The LinuxBoot Server designation is to ensure a server platform is suitable for deployment on the LinuxBoot firmware stack, the IR designation is for devices in the IoT edge sector and the SR is for deploying Arm servers. Embedded server (ES) designation is for deploying server workloads in Arm-based processors in edge compute platforms. There are two components to the ES designation. The base system architecture (BSA) defines the minimum hardware requirement to deploy an operating system. The base boot requirement (BBR) is the firmware component that provides a standard firmware interface to the operating system. The architecture compliance suite validates BSA at the hardware level and has many tests that cover the various aspects of the BBR.

NXP design platform LX2160RDB is currently certified as SystemReady ES. The LS1046A FRWY board and LS1043ARDB are currently in the process of getting certified. These platforms offer seamless interoperability with the standard operating systems and hypervisors such as VMware ESXi-Arm Fling v1.1, Ubuntu Server 20.04, Fedora Server 32, Debian 10.4.0, CentOS 8.2, OpenSUSE Leap 15.2 and Windows PE. This allows us to empower our partners and customers with an out-of-box solution to deploy server workloads with confidence.

Product Marketer, NXP Semiconductor

Ghoshank Patel is a product marketer for NXP Network Edge Processing Group. He holds a Bachelor of Science in Electrical and Computer Engineering from the University of Texas at Austin.