SuperSpeed USB 3.0 Redriver

お客様の素早い設計とより早い製品化を実現する、技術情報と専門知識をご紹介します。

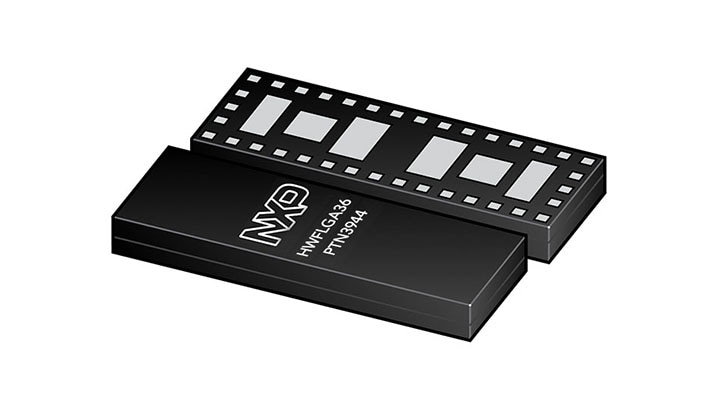

PTN3944は、PCIe 4.0、UPI、および類似の高速インターフェース向けに最適化された高性能マルチチャネル (x4) リニア・イコライザです。PTN3944は、PCIeおよびUPIインターフェースの実装に要求される高速信号の品質向上に対応しています。

このデバイスは、ピン・ストラッピングまたはI²C制御によって出力信号スイングのリニアリティを制御するプログラマブル・リニア・イコライゼーションを備えており、シンボル間干渉 (ISI) を抑制することで、シグナル・インテグリティの向上およびチャネルの拡張を可能にします。このイコライザは、幅広いチャネル条件での使用をサポートしています。PTN3944は、I²Cレジスタへの書込みを使用してディープ・スタンバイ状態への切り替えをサポートします。

PTN3944は1.8 V電源で動作します。パッケージには小型で高性能なHWFLGA36を採用しています。

SuperSpeed USB 3.0 Redriver

マルチプロトコルUSB 4 20 Gbpsリニア・リドライバ

|

|

|

|

|

|

|

|---|---|---|---|---|---|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

クイック・リファレンス ドキュメンテーションの種類.

3 ドキュメント

セキュアファイルの読み込み中、しばらくお待ちください。