QorIQ® P4080/P4040/P4081 Multicore Communications Processors

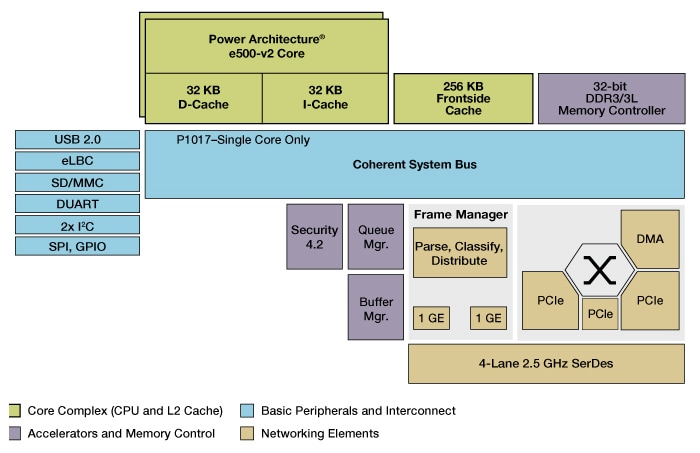

The P1023 and P1017 processors offer the value of integrated high-performance data path offload for networking protocols and dual e500 Power Architecture® cores for application software. The P1023 and P1017 are ideally suited for high-performance enterprise WLAN, fixed routers and security gateway applications. The P1023 device supports a 400–800 MHz performance range, along with advanced security and a rich set of interfaces—all delivered on 45 nm technology for low-power implementation.

The P1023 processor includes a performance-optimized implementation of the QorIQ® data path acceleration architecture (DPAA). This architecture provides the infrastructure to support simplified sharing of networking interfaces and accelerators by multiple CPU cores. The DPAA significantly reduces software overhead associated with high touch packet forwarding operations. Examples of the types of packet processing services this architecture is optimized to support include traditional routing and bridging, firewall, VPN termination for IPsec and MACsec (a standardized form of Ethernet encapsulation that can be used to provide confidentiality).

注: 製品の特徴を見るには、このウィンドウを閉じます。.

|

|

|

|

|

|

|

|---|---|---|---|---|---|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P1023クイック・リファレンス ドキュメンテーションの種類.

1-10 / 37 ドキュメント

コンパクトリスト

この選択アイテムには該当する結果がありません。

セキュアファイルの読み込み中、しばらくお待ちください。

1-10 の 37 ドキュメント

コンパクトリスト

クイック・リファレンス ソフトウェア・タイプ.

3 ソフトウェア・ファイル

注: より快適にご利用いただくために、ソフトウェアのダウンロードはデスクトップで行うことを推奨します。

セキュアファイルの読み込み中、しばらくお待ちください。

3 ソフトウェア・ファイル

注: より快適にご利用いただくために、ソフトウェアのダウンロードはデスクトップで行うことを推奨します。

1 トレーニング

1 トレーニング

There are no recently viewed products to display.

閲覧履歴を表示または編集する