USB PDおよびType-C電流制限電源スイッチ

動画の上をクリックすると再生されます。

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

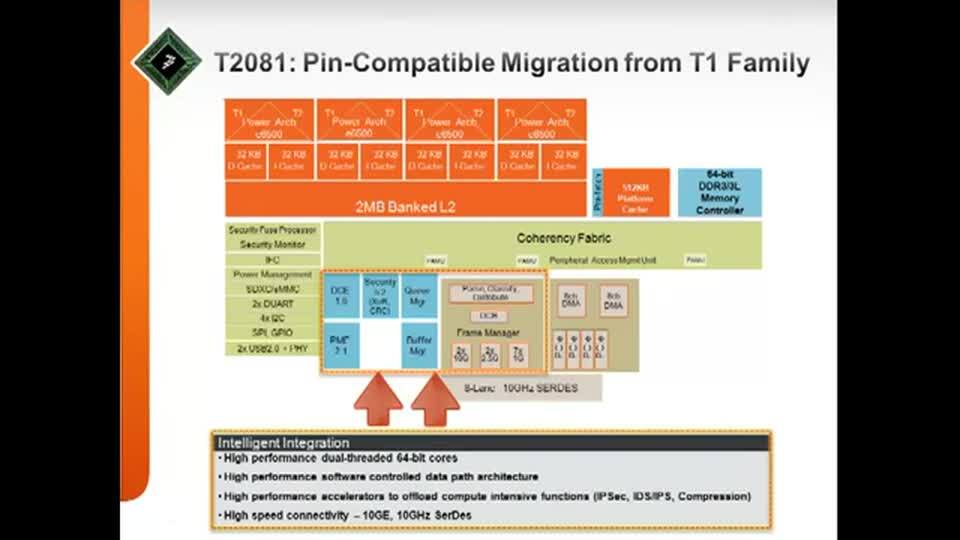

The QorIQ T1042 quad-core and T1022 dual-core communication processors support two or four integrated 64-bit e5500 Power Architecture® processor cores with high-performance data path acceleration architecture (DPAA) and network peripheral interfaces required for networking and telecommunications.

The T1 family of devices is a scalable, pin-compatible family of communications processors – and offers pin-compatible migration up to the higher-performance QorIQ T2081 device.

| T1020 | T1022 | T1040 | T1042 | T2081 | |

|---|---|---|---|---|---|

| CPU | 2 e5500 | 2 e5500 | 4 e5500 | 4 e5500 | 4 e6500 (dual-threaded) |

| Core Frequency | 1200-1400MHz | 1200-1400MHz | 1200-1400MHz | 1200-1400MHz | 1500-1800MHz |

| DDR I/F | 1x DDR3L/4 to 1600MT/s | 1x DDR3L/4 to 1600MT/s | 1x DDR3L/4 to 1600MT/s | 1x DDR3L/4 to 1600MT/s | 1x DDR3/3L to 2133MT/s |

| Ethernet (with IEEE1588v2) | 8-Port GE Switch + 4x 1GE | 5x 1GE | 8-Port GE Switch + 4x 1GE | 5x 1GE | 2x 1/10GE + 6x 1GE |

| SERDES | 8 lanes (5GHz) | 8 lanes (5GHz) | 8 lanes (5GHz) | 8 lanes (5GHz) | 8 lanes (10GHz) |

| Package | Pin Compatible | ||||

USB PDおよびType-C電流制限電源スイッチ

Bidirectional High-Side Power Switch for Charger and USB‑OTG Combined Applications

オープン・ドレインおよびプッシュ・プル・アプリケーション向け双方向電圧レベル変換器

SMBus対応の8ピン・リモート/ローカル・デジタル温度センサ

| | | | | |

|---|---|---|---|---|---|

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

T1042クイック・リファレンス ドキュメンテーションの種類.

1-10 / 23 ドキュメント

コンパクトリスト

この選択アイテムには該当する結果がありません。

セキュアファイルの読み込み中、しばらくお待ちください。

1-10 の 23 ドキュメント

コンパクトリスト

5 ハードウェア提供

この製品をサポートするその他のパートナー製品を見つけるには、当社の Web サイトにアクセスしてください パートナーマーケットプレイス.

2 ハードウェア提供

クイック・リファレンス ソフトウェア・タイプ.

3 ソフトウェア・ファイル

注: より快適にご利用いただくために、ソフトウェアのダウンロードはデスクトップで行うことを推奨します。

セキュアファイルの読み込み中、しばらくお待ちください。

3 ソフトウェア・ファイル

注: より快適にご利用いただくために、ソフトウェアのダウンロードはデスクトップで行うことを推奨します。

3 エンジニアリング・サービス

There are no results for this selection.

There are no results for this selection.

この製品をサポートするその他のパートナー製品を見つけるには、当社の Web サイトにアクセスしてください パートナーマーケットプレイス.

2 トレーニング

2 トレーニング

There are no recently viewed products to display.

閲覧履歴を表示または編集する