アプリケーション・ノート (1)

サポート情報 (1)

-

SPIFI Library - Release Notes[SPIFI-NXP-MICROCONTROLLERSRN]

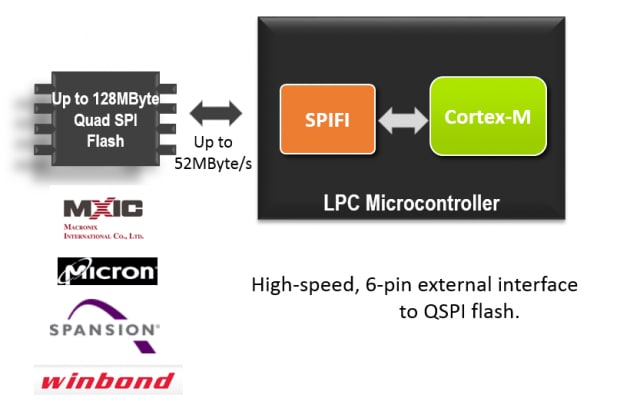

The SPI Flash Interface (SPIFI) allows low pin-count serial flash memories to be connected to an Arm® based LPC Microcontroller with very little performance penalty compared to higher pin-count parallel flash memories. After a few commands configure the interface at startup,the entire flash content is accessible as normal memory using byte, halfword, and word accesses by the processor and/or DMA channels.Erasure and programming are handled by simple sequences of commands.

Many SPI flash devices use serial commands for device setup/initialization, and then move to dual or quad commands for normal operation. Different serial Flash vendors and devices accept or require different commands and command formats. SPIFI includes sufficient flexibility to be compatible with many market-leading devices plus extensions to help insure compatibility with future devices.

The SPIFI implements basic, dual, and quad SPI in half-duplex mode, in which the SPIFI always sends a command to a serial flash memory at the start of each frame. In write commands, the SPIFI sends all of the data in the frame, while in read commands, the SPIFI sends the command, and then the serial flash sends data to the SPIFI. SPI Flash devices respond to commands sent by software, or automatically sent by the SPIFI when software reads the serial flash region of the memory map. Commands are divided into fields called opcode, address, intermediate data, and data. The address,intermediate data, and data fields are optional depending on the opcode. Some devices include a mode in which the opcode can be implied in Read commands for higher performance. Data fields are further divided into input and output data fields depending on the opcode.

注: ソフトウェアの機能を見るには、このウィンドウを閉じます。.

LPC1800/4300 devices support boot from flash.The boot code sets the SPIFI clock to 32 MHz at the beginning of the boot process and checks for the type of SPI flash device. If the detected device is unknown, the SPIFI clock is reduced to 18 MHz,otherwise device boot with a SPIFI clock of 32MHz

| Device | Boot Support | Exit from no opcode mode | Comments |

| Chingis | PM25LD040, PM25LD010C, PM25LD020C, PM25LD512C, PM25LD256C, PM25LQ032C | Yes | |

| Giga Device | GD25Q80 | Yes | |

| Macronix | MX25L6435E, MX25L8006E, MX25L1606E, MX25L8035E, MX25L1633E, MX25L3235E, MX25L6435E, MX25L12835E, MX25L25635E, MX1635E | Yes | |

| MX25L12835F, MX25L25635F | Yes | These devices take longer time to be ready after power on. You may need to delay the startup of LPC18xx/LPC43xx.One way to achieve this sequence is to delay RESETN signal of LPC18xx/LPC43xx. | |

| Micron | M25PX80, M25PX16, M25PX32, M25PX64, M25P10, M25P16, M25P32, M25P64, M25P80 | Yes | |

| N25Q032A, N25Q064A, N25Q128A, N25Q256A | No* | LPC18xx/LPC43xx support cold boot with these devices. May not boot when LPC18xx/LPC43xx is reset and serial flash is in no Opcode mode. In case of planned reset, MCU can get serial flash out of No Opcode mode before resetting itself. | |

| Spansion | S25FL032P, S25FL064P, S25FL128S, S25FL256S, S25FL256S, S25FL129P, S25FL004K, S25FL008K

S25FL016K, S25FL032K, S25FL064K, S25FL116K, S25FL132K, S25FL164K,S25FL127S |

Yes | |

| SST(Microchip) | SST25VF064,SST25VF016 | Yes | |

| Winbond | W25Q80BV,W25Q16DV,W25Q32FV,W25Q64FV,W25Q128FV,W25Q256FV, W25Q32JVSIQ, W25Q64JVSIQ | Yes |

Remarks: To boot from serial flashes, it is recommended that customers fully characterize the timing in their applications.

3 ダウンロード

There are no results for this selection.

注: より快適にご利用いただくために、ソフトウェアのダウンロードはデスクトップで行うことを推奨します。

セキュアファイルの読み込み中、しばらくお待ちください。

3 ダウンロード

注: より快適にご利用いただくために、ソフトウェアのダウンロードはデスクトップで行うことを推奨します。

SPIFI-NXP-MICROCONTROLLERSクイック・リファレンス ドキュメンテーションの種類.

2 ドキュメント

コンパクトリスト

この選択アイテムには該当する結果がありません。

セキュアファイルの読み込み中、しばらくお待ちください。

2 ドキュメント

コンパクトリスト

There are no recently viewed products to display.

閲覧履歴を表示または編集する