EdgeLock® Assurance

The TJA1153, part of the EdgeLock Assurance program, is designed to meet industry standards and follows NXP's security-by-design approach.

画像にカーソルを合わせると拡大表示されます。

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

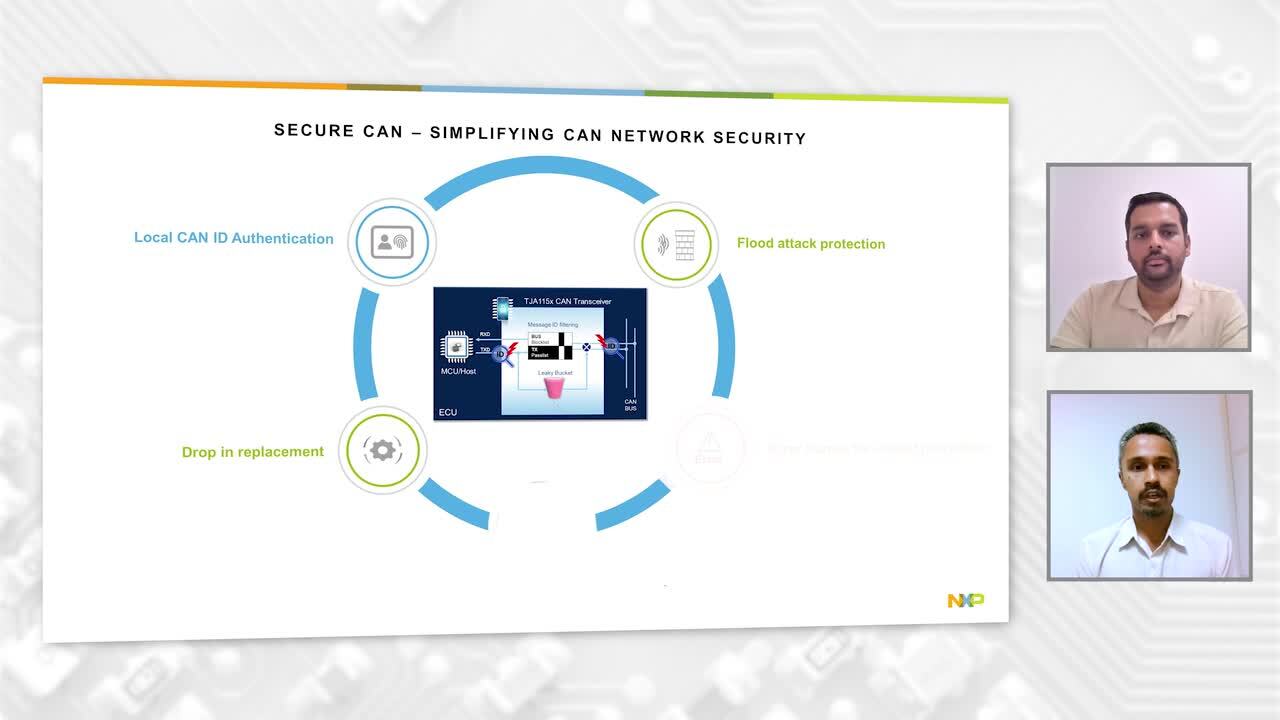

NXP's new secure CAN transceiver TJA1153A provides a seamless and very cost-effective solution for securing classical CAN and CAN FD communication without cryptography. The TJA1153A belongs to a new generation of automotive high-speed CAN/CAN FD transceivers, offering security functions. It provides an interface between a classical CAN or CAN FD protocol controller and the physical two-wire CAN bus. As long as no security incidents have been detected, the TJA1153A behaves like a standard CAN transceiver with Sleep mode.

The security incidents that can be detected and contained are:

The TJA1153, part of the EdgeLock Assurance program, is designed to meet industry standards and follows NXP's security-by-design approach.

1 結果

マッチしていない 0 NRND

パーツ | 注文 | コンピュータ支援設計 モデル | 状況 | パッケージタイプ | Package Pitch (mm) | Recommended Orderable Part Number | MCU I/O Interface (V) | VIO Option Available | Low Power Modes | データ・レート(最大)(Kbps) | CAN Channels | 製品カテゴリー | 電源電圧 [最小 - 最大] (V) | データ・レート(最小)(Kbps) | Voltage on bus pins [Min-Max] (V) | VESD IEC on bus pins (+/- kV) | VESD HBM on bus pins (+/- kV) | Junction Temperature (Max) (℃) | 保護 | Wake-Up Pin | Min High Input Levels (V) [Vio] | Supported standards | SPLIT Pin | Thermal Resistance (Spec) (℃/W) | Product Application |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

アクティブ | HVSON14 | 0.65 | TJA1153ATK/0Z | 3.3, 5.0 | Y | Sleep Mode, Standby Mode | 5000.0 | 1 | Secure CAN / High-Speed CAN / CAN FD | 4.75 to 5.25 | 40.0 | -58 to 58 | 0 to 0 | 0 to 0 | 150 | TXD dominant timeout, overtemperature, undervoltage | Y | 2.1 | ISO-11898-2:2016, SAE J2284-1, SAE J2284-2, SAE J2284-3, SAE J2284-4, SAE J2284-5 | N | 50 | Automotive, Industrial |

TJA1153クイック・リファレンス ドキュメンテーションの種類.

3 ドキュメント

コンパクトリスト

この選択アイテムには該当する結果がありません。

サインイン 許可されたセキュアファイルにアクセス。について詳しくはこちら セキュアなアクセス権.

セキュアファイルの読み込み中、しばらくお待ちください。

3 ドキュメント

コンパクトリスト

クイック・リファレンス ソフトウェア・タイプ.

サインイン 許可されたセキュアファイルにアクセス。について詳しくはこちら セキュアなアクセス権.

セキュアファイルの読み込み中、しばらくお待ちください。

There are no recently viewed products to display.

閲覧履歴を表示または編集する