Low-Ohmic Four-Pole Double-Throw Analog Switch

動画の上をクリックすると再生されます。

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

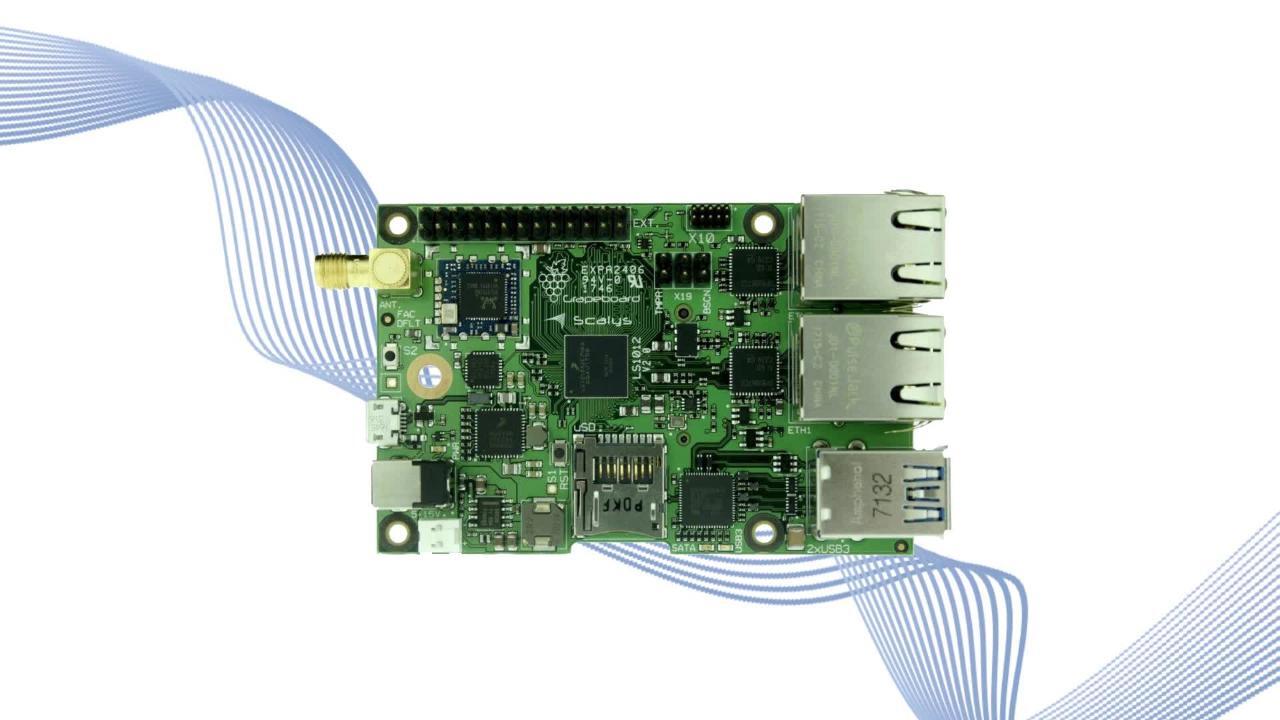

The LS1012A processor, optimized for battery-backed or USB-powered, space-constrained networking and IoT applications, integrates a single Arm® Cortex®-A53 core running up to 1GHz with a hardware packet forwarding engine and high-speed interfaces to deliver line-rate networking performance in an ultra-small size envelope at 1W typical power dissipation. The LS1012A incorporates the same Trust Architecture and software compatibility of higher-tier LS family devices, enabling scalable, secure applications that leverage a common 64-bit software platform.

Layerscape processors are part of NXP's EdgeVerse™ edge computing platform.

低電圧変換16ビットI²Cバス/SMBus I/Oエキスパンダ

オープン・ドレインおよびプッシュ・プル・アプリケーション向け双方向電圧レベル変換器

16ビットI²CバスおよびSMBus I/Oポート(割込み対応)

USB PDおよびType-C電流制限電源スイッチ

Bidirectional High-Side Power Switch for Charger and USB‑OTG Combined Applications

Dual-Supply Translating Transceiver (Open-Drain, Auto-Direction Sensing)

1-10 の 12 結果

マッチしていない 8 NRND

パーツ | 注文 | コンピュータ支援設計 モデル | Silicon Rev | ファミリー | 状況 | 開発ツール | 製品認証 | 標準価格 | パッケージ端子数 | パッケージタイプ | Package Pitch (mm) | コア・タイプ | コア:コア数 - 仕様 | 動作周波数[最大](MHz) | Typical Power | Cache (KB) | L1 Cache (KB) | L2 Cache (Max) (KB) | SRAM (kB) | 対応する外部メモリ | DRAM frequency (max)(MHz) | Serial Audio Interface (SAI) | I2S | SPI | QSPI | UART | I2C | USB Controllers | Ethernet Ports | イーサネット・タイプ | PCIe | SATA | Encryption | Watchdog timer | タイマー | デバッグ & トレース | Junction Temperature (Min to Max) (℃) |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

Rev 2 | QorIQ LS1012A | アクティブ | LS1012A-RDB | Industrial | 1K @ US$13.22 | 211 | VFLGA211 | 0.5 | Arm Cortex-A53 | 1 | 600 | 1.14 | 32 | 32 | 256 | 128 | DDR3L SDRAM | 1000 | 5 | 5 | 1 | 1 | 2 | 2 | 2 | 2 | 100M, 10M, 1G, 2.5G | 1 | 1 x SATA 3.0 | Y | Y | 2 | JTAG | 0 to 105 | |||

Rev 2 | QorIQ LS1012A | アクティブ | LS1012A-RDB | Industrial | 1K @ US$14.55 | 211 | VFLGA211 | 0.5 | Arm Cortex-A53 | 1 | 800 | 1.17 | 32 | 32 | 256 | 128 | DDR3L SDRAM | 1000 | 5 | 5 | 1 | 1 | 2 | 2 | 2 | 2 | 100M, 10M, 1G, 2.5G | 1 | 1 x SATA 3.0 | Y | Y | 2 | JTAG | 0 to 105 | |||

Rev 2 | QorIQ LS1012A | アクティブ | LS1012A-RDB | Industrial | 1K @ US$16.01 | 211 | VFLGA211 | 0.5 | Arm Cortex-A53 | 1 | 1000 | 1.26 | 32 | 32 | 256 | 128 | DDR3L SDRAM | 1000 | 5 | 5 | 1 | 1 | 2 | 2 | 2 | 2 | 100M, 10M, 1G, 2.5G | 1 | 1 x SATA 3.0 | Y | Y | 2 | JTAG | 0 to 105 | |||

Rev 2 | QorIQ LS1012A | アクティブ | LS1012A-RDB | Industrial | 1K @ US$12.60 | 211 | VFLGA211 | 0.5 | Arm Cortex-A53 | 1 | 600 | 1.14 | 32 | 32 | 256 | 128 | DDR3L SDRAM | 1000 | 5 | 5 | 1 | 1 | 2 | 2 | 2 | 2 | 100M, 10M, 1G, 2.5G | 1 | 1 x SATA 3.0 | N | Y | 2 | JTAG | 0 to 105 | |||

Rev 2 | QorIQ LS1012A | アクティブ | LS1012A-RDB | Industrial | 1K @ US$13.87 | 211 | VFLGA211 | 0.5 | Arm Cortex-A53 | 1 | 800 | 1.17 | 32 | 32 | 256 | 128 | DDR3L SDRAM | 1000 | 5 | 5 | 1 | 1 | 2 | 2 | 2 | 2 | 100M, 10M, 1G, 2.5G | 1 | 1 x SATA 3.0 | N | Y | 2 | JTAG | 0 to 105 | |||

Rev 2 | QorIQ LS1012A | アクティブ | LS1012A-RDB | Industrial | 1K @ US$15.24 | 211 | VFLGA211 | 0.5 | Arm Cortex-A53 | 1 | 1000 | 1.26 | 32 | 32 | 256 | 128 | DDR3L SDRAM | 1000 | 5 | 5 | 1 | 1 | 2 | 2 | 2 | 2 | 100M, 10M, 1G, 2.5G | 1 | 1 x SATA 3.0 | N | Y | 2 | JTAG | 0 to 105 | |||

Rev 2 | QorIQ LS1012A | アクティブ | LS1012A-RDB | Industrial | 1K @ US$14.55 | 211 | VFLGA211 | 0.5 | Arm Cortex-A53 | 1 | 600 | 1.14 | 32 | 32 | 256 | 128 | DDR3L SDRAM | 1000 | 5 | 5 | 1 | 1 | 2 | 2 | 2 | 2 | 100M, 10M, 1G, 2.5G | 1 | 1 x SATA 3.0 | Y | Y | 2 | JTAG | -40 to 105 | |||

Rev 2 | QorIQ LS1012A | アクティブ | LS1012A-RDB | Industrial | 1K @ US$16.01 | 211 | VFLGA211 | 0.5 | Arm Cortex-A53 | 1 | 800 | 1.17 | 32 | 32 | 256 | 128 | DDR3L SDRAM | 1000 | 5 | 5 | 1 | 1 | 2 | 2 | 2 | 2 | 100M, 10M, 1G, 2.5G | 1 | 1 x SATA 3.0 | Y | Y | 2 | JTAG | -40 to 105 | |||

Rev 2 | QorIQ LS1012A | アクティブ | LS1012A-RDB | Industrial | 1K @ US$17.61 | 211 | VFLGA211 | 0.5 | Arm Cortex-A53 | 1 | 1000 | 1.26 | 32 | 32 | 256 | 128 | DDR3L SDRAM | 1000 | 5 | 5 | 1 | 1 | 2 | 2 | 2 | 2 | 100M, 10M, 1G, 2.5G | 1 | 1 x SATA 3.0 | Y | Y | 2 | JTAG | -40 to 105 | |||

Rev 2 | QorIQ LS1012A | アクティブ | LS1012A-RDB | Industrial | 1K @ US$13.87 | 211 | VFLGA211 | 0.5 | Arm Cortex-A53 | 1 | 600 | 1.14 | 32 | 32 | 256 | 128 | DDR3L SDRAM | 1000 | 5 | 5 | 1 | 1 | 2 | 2 | 2 | 2 | 100M, 10M, 1G, 2.5G | 1 | 1 x SATA 3.0 | N | Y | 2 | JTAG | -40 to 105 |

LS1012Aクイック・リファレンス ドキュメンテーションの種類.

1-10 / 27 ドキュメント

コンパクトリスト

この選択アイテムには該当する結果がありません。

サインイン 許可されたセキュアファイルにアクセス。について詳しくはこちら セキュアなアクセス権.

セキュアファイルの読み込み中、しばらくお待ちください。

1-10 の 27 ドキュメント

コンパクトリスト

完全な内訳を受け取ります。 eCad ファイルで製品のフットプリントなどを確認してください。

5 ハードウェア提供

追加ハードウェアを利用可能 パートナー・ソリューションの特集を表示.

サインイン 許可されたセキュアファイルにアクセス。について詳しくはこちら セキュアなアクセス権.

1-5 の 10 ハードウェア提供

この製品をサポートするその他のパートナー製品を見つけるには、当社の Web サイトにアクセスしてください パートナーマーケットプレイス.

5 ハードウェア提供

追加ハードウェアを利用可能 パートナー・ソリューションの特集を表示.

クイック・リファレンス ソフトウェア・タイプ.

1-5 の 7 ソフトウェア・ファイル

追加ソフトウェアを利用可能 パートナー・ソリューションの特集を表示.

注: より快適にご利用いただくために、ソフトウェアのダウンロードはデスクトップで行うことを推奨します。

サインイン 許可されたセキュアファイルにアクセス。について詳しくはこちら セキュアなアクセス権.

セキュアファイルの読み込み中、しばらくお待ちください。

1-5 の 7 ソフトウェア・ファイル

追加ソフトウェアを利用可能 パートナー・ソリューションの特集を表示.

注: より快適にご利用いただくために、ソフトウェアのダウンロードはデスクトップで行うことを推奨します。

3 エンジニアリング・サービス

There are no results for this selection.

There are no results for this selection.

この製品をサポートするその他のパートナー製品を見つけるには、当社の Web サイトにアクセスしてください パートナーマーケットプレイス.

4 トレーニング

追加トレーニングを利用可能 View our featured partner trainings.

4 トレーニング

追加トレーニングを利用可能 View our featured partner trainings.